## PHD DISSERTATION

Enhancing Formal Modelling Tool Support with Increased Automation

by Kenneth Lausdahl

Enhancing Formal Modelling Tool Support with Increased Automation

# Enhancing Formal Modelling Tool Support with Increased Automation

PhD Thesis by

Kenneth Lausdahl

Aarhus University Department of Engineering, Denmark

ISBN 978-87-93102-02-6 (e-book)

Published, sold and distributed by: River Publishers P.O. Box 1657 Algade 42 9000 Aalborg Denmark

Tel.: +45369953197 www.riverpublishers.com

Copyright for this work belongs to the author, River Publishers have the sole right to distribute this work commercially.

All rights reserved © 2013 Kenneth Lausdahl.

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without prior written permission from the Publisher.

### Abstract

The intrinsic complexity of even simple software systems makes their development challenging. This is especially true for heterogeneous embedded control systems that include the constraints of the physical world. Formal methods and modelling techniques allow software designs to be analysed and thus contribute to their reliability and robustness. However, industrial adoption of formal methods is limited by uncertainties related to their cost, effectiveness and the skills required. This thesis has three areas of focus: manual labour reduction through automation of various kinds of analysis, with focus on validation; language translation utilised to exploit existing automated analysis techniques; and a way to model and simulate embedded control systems that demand high-fidelity representation of their environment, based on a sound formal foundation. The result is a collection of contributions to a modern integrated development environment that can analyse software specifications and simulate hybrid embedded control systems with their environment.

## Resumé

Udviklingen af selv små software systemer er en kompleks udfordring: især for heterogene indlejrede kontrolsystemer, som også tager højde for dynamikken i den fysiske verden. Formelle metoder og tilsvarende modelleringsteknikker muliggør analyse af software design. Det kan være medvirkende til at øge pålideligheden og derved sikre et mere robust system. Dog har den industrielle anvendelse af formelle metoder været begrænset, primært grundet usikkerhed i forhold til omkostningerne og den nødvendige tekniske ekspertise.

Denne afhandling har tre fokus områder: reduktion af manuelt arbejde gennem automatisering af forskellige former for analyser primært med fokus på validering; udnyttelse af eksisterende automatiserede analyse teknikker ved hjælp af sprog oversættelse; og simulering af indlejrede kontrolsystemer, der kræver en meget detaljeret og nøjagtig repræsentation af det dynamiske miljø systemet opererer i. Der præsenteres adskillige bidrag til analyse af software abstraktioner som alle bidrager til et moderne integreret udviklingsmiljø.

### Acknowledgements

I would like to thank my supervisor Peter Gorm Larsen from the Department of Engineering, University of Aarhus, for providing valuable feedback during my PhD. It has been a great pleasure and great continuous source of inspiration to work with Peter, who always sees opportunities. His professionalism and dedication is second to none. I would also like to thank my co-supervisor Erik Ernst from the Computer Science Department, University of Aarhus, for his impressive sense for detail and feedback that he has provided during the development of this PhD thesis.

I give thanks to the DESTECS project for funding my PhD. I have had so many useful discussions with this group of talented people, who have also given me the opportunity to get valuable feedback from industrial partners. I would like to give a special thanks to my colleagues in the DESTECS project at Controllab Products Peter Visser and Frank Groen.

I would like to express my gratitude to Daniel Jackson and his software design group at the Computer Science and Artificial Intelligence Lab at Massachusetts Institute of Technology for giving me the opportunity to visit them in Cambridge, MA, USA, and to Aarhus university research foundation and Fondation Idella for providing the necessary funding this trip.

I would also like to thank all my close collaborators: Nick Battle, Joey W. Coleman and Augusto Ribeiro. The collaboration with these skilled people have helped me develop my competences as a researcher. I have enjoyed our many valuable discussions that have given served as inspiring variation. In particular, I admire their dedication to detail.

I would like to thank Claus Ballegaard Nielsen and Sune Wolff for their camaraderi and many small interactions as well as the feedback they have provided during the development of this PhD thesis. I would also like to thank Stefan Hallerstede for his valuable feedback and review of this PhD thesis.

I would like to thank my parents, Yvonne and Henning Lausdahl, for loving and supporting me unconditionally, and for giving me a good foundation for life. I also thank my sister Leni Lausdahl, for being the best sister

#### x Acknowledgements

in the world. My family has been a source of constant encouragement and unconditional support.

Last, but not least, I would like to thank my beautiful wife Tenna Lausdahl for her love, support and can-do spirit. I would especially like to thank her for giving my two wonderful daughters, Marie and Laura, the apples of my eye and a constant source of smiles. I would also like to thank the three of them for joining me on multiple occasions when research has lead me abroad. This thesis is dedicated to my wife and my two daughters.

# Contents

| Ał     | Abstract     |                                                           |    |  |  |

|--------|--------------|-----------------------------------------------------------|----|--|--|

| Resumé |              |                                                           |    |  |  |

| Ac     | know         | ledgements                                                | ix |  |  |

| I      | Ove          | erview                                                    | 1  |  |  |

| 1      | Introduction |                                                           |    |  |  |

|        | 1.1          | Modelling of Software Systems                             | 4  |  |  |

|        | 1.2          | Formal Modelling Languages                                | 5  |  |  |

|        | 1.3          | Modelling of Physical Systems                             | 9  |  |  |

|        | 1.4          | Motivation                                                | 11 |  |  |

|        | 1.5          | Research Method                                           | 11 |  |  |

|        | 1.6          | Research Objectives                                       | 12 |  |  |

|        | 1.7          | Evaluation Criteria                                       | 13 |  |  |

|        | 1.8          | Published Work                                            | 14 |  |  |

|        | 1.9          | Outline and Reading Guide                                 | 17 |  |  |

| 2      | Tool         | Automation                                                | 19 |  |  |

|        | 2.1          | Overture in a Historical Perspective                      | 19 |  |  |

|        | 2.2          | Development                                               | 21 |  |  |

|        | 2.3          | Validation                                                | 22 |  |  |

|        | 2.4          | Translation                                               | 38 |  |  |

|        | 2.5          | Formal Verification                                       | 43 |  |  |

| 3      | Semantics    |                                                           |    |  |  |

|        | 3.1          | Existing VDM Semantics Efforts                            | 47 |  |  |

|        | 3.2          | The VDM Real-Time Semantics Developed in this PhD Project | 49 |  |  |

|        | 3.3          | Co-Simulation Semantics                                   | 52 |  |  |

#### xii Contents

| 4   | Conclusion                         |                                                      |    |  |

|-----|------------------------------------|------------------------------------------------------|----|--|

|     | 4.1                                | Introduction                                         | 59 |  |

|     | 4.2                                | Research Contributions                               | 59 |  |

|     | 4.3                                | Evaluation of Contributions                          | 61 |  |

|     | 4.4                                | Future Work                                          | 65 |  |

| Π   | Puł                                | olications                                           | 69 |  |

| 5   | The                                | Overture Initiative – Integrating Tools for VDM      | 71 |  |

| 6   | Con                                | necting UML and VDM++ with Open Tool Support         | 73 |  |

| 7   | Tran                               | slating VDM to Alloy                                 | 75 |  |

| 8   | A Deterministic Interpreter        |                                                      |    |  |

| 9   | Combinatorial Testing for VDM      |                                                      |    |  |

| 10  | Combining VDM with Executable Code |                                                      | 81 |  |

| 11  | Run                                | Time Validation of Timing Constraints for VDM Models | 83 |  |

| 12  | Sema                               | antics Focused Papers                                | 85 |  |

| Bil | Bibliography                       |                                                      |    |  |

# Part I

# Overview

# 1

## Introduction

People are surrounded by devices that contain software, and daily life is becoming increasingly more dependent upon the services offered by software in general. However, a common practice in some areas of the software industry is to release incomplete software, or software with known faults to gain a market advantage. This is made even worse by the constantly increasing complexity of software, while at the same time expectations are that it performs flawlessly. Unfortunately, this is not the case, and most software is faulty and expensive to develop partially due to the increase in complexity. Faulty software poses a significant risk in safety critical systems where either machinery or humans might be damaged or hurt by errors. The consequence of the increase in complexity and expectations is that a large number of software projects fail and either get cancelled or run over budget, and still deliver fewer features than initially claimed [136, 59].

The software engineering discipline is relatively new compared to other disciplines such as mechanical engineering that dates back to the medieval times and was deeply influenced by the work of Archimedes (287 BC) and later Heron of Alexandria (c. 10-70 AD) who created the first steam engine. The mechanical engineering discipline uses modelling techniques to accurately predict the behaviour of a final system. This ability to accurately design and later build the same solution still remains unsolved for software engineering.

The term *software engineering* was introduced in the 1968 NATO Software Engineering Conference [106], 45 years ago; where concepts were introduced for software development. Unfortunately, the concepts introduced at that conference are not universally used in software development. The modelling concept allows engineers to formally describe software systems based on their informal requirements and thus unambiguously capture interactions with devices external to the system; the result is a formal specification that thus can be analysed. The specification can then be *validated* against the

informal requirements by simulation, thus checking that the specification represents the intended system. A specification can also be *verified* with respect to its internal consistency by e.g. checking for contradictions in the form of type incomparability, conflicting invariants etc. These types of analysis are challenging to perform by hand and, therefore, automated analysis is a significant advantage since it reduces human errors and in most cases speeds up analysis by an order of magnitude [129].

#### 1.1 Modelling of Software Systems

Modelling is the process of capturing and describing knowledge about a system in an abstract form. The result is a *specification* that capture the requirements for a given system and its behaviour. A specification is described using a modelling language that focuses on certain types of analysis. Various modelling languages exist which can be used to describe a system; the languages can either be graphical using diagrammatic techniques (e.g. the Unified Modelling Language), or textual using standardized keywords in a natural language or with terms that make the language interpretable by computers. These interpretable languages can be formal modelling languages with a concrete syntax and well defined semantics that is built on mathematics and therefore provides a base of analysis.

The nature of a system may favour some modelling languages over others, e.g. a software ticketing system might require a language capable of describing relations, while an embedded reactive control system might require the ability to describe the complex behaviour of the controller in the system but also the ability to faithfully represent the physical environment it operates within. The first case of a simple software system may be modelled by any of the languages like: UML, Alloy, Z, B or VDM from the discrete-event (DE) domain; however, the second category requires a more complex language that not only has the capability to describe elements of the DE domain but also the ability to describe physical elements of the environment, that belong to the continuous-time (CT) domain. To describe such systems a language that spans multiple domains is needed either in the form of a single language or two languages that integrate with each other.

The motivation behind the creation of a specification of a system is to describe the system in a clear and concise way and then through analysis check that the specification is consistent and unambiguous and reflects the requirements. A critical factor is the ability to automatically check such specifications for internal consistency and validation against external criteria e.g. requirements. This is supported by formal modelling languages due to their mathematical foundations.

#### 1.2 Formal Modelling Languages

This section gives a brief description of a few of the existing formal modelling languages (Z, B, Event-B, Alloy and VDM) which have been used both in academia and industry. The formalisms are presented with a description of the available tools that can be used for various kinds of analysis. The section presents an extended description of VDM which is the language used throughout this thesis.

#### 1.2.1 Z-notation

The Z-notation was developed at Oxford University in the 1980's; it was originally proposed by Jean-Raymond Abrial in 1977, based on the publication [2]. The Z-notation was later ISO standardised [56], a number of books have been written about the Z-notation [58, 122, 156, 158]. It is based on the standard mathematical notation used in axiomatic set theory, lambda calculus and first-order predicate logic. The logic is augmented with structure (*schemas*) to make it easy to describe software systems, i.e. *schema calculus*. Specifications are built as a collection of schemas. The most popular version of Z is the version from Mike Spivey's book [134]. Z, unlike B, does not have built-in refinement, and thus many users view Z as a system modelling language and have no intent of proving the conformance of code to the specification. However, a well-established theory to refinement of Z exists, as introduced in Woodcock's book [156]

#### Tools for Z

The tools available for Z focuses on theorem proving. The most widely used proof tools are ProofPower from Lemma 1 Ltd., and Z/Eves, a front-end to the Eves theorem prover from ORA Canada. Eves can calculate preconditions and perform domain checks (checking that partial functions are not applied outside their domain) as well as general theorem proving. The tool is automated but still requires expert assistance. Mark Utting has developed an animator for Z named Jaza<sup>1</sup>. It can execute operations written in an explicit style, evaluate expressions, check state against invariants, and so on. Finally,

<sup>1</sup> http://www.cs.waikato.ac.nz/~marku/jaza/

the Community Z Tools (CTZ)  $project^2$  aims to combine tools for Z. The tool currently includes infrastructure required to parse, type check, edit and animate Z (ALive).

#### 1.2.2 B-Method and Event-B

The B-Method [1] is a method for software development based on the B notation, it is based around an abstract machine notation for e.g. embedded software development. The method was originally developed by Jean-Raymond Abrial and is a proof-based refinement method. The B notation is related to Z, but B is closer to the implementation level, with focus on formal refinement to code compared to just formal specification. The formal method Event-B [3] is an evolution of B and has a simpler notation. It focuses more on system-level modelling, and is thus less suited for embedded software. Event-B is also a refinement method, and it has been used in the DEPLOY project<sup>3</sup> [130, 129]. Furthermore, Event-B forms the base in a current research project Advanced Design and Verification Environment for Cyber-physical System Engineering (ADVANCE<sup>4</sup>).

#### Tools for B and Event-B

The B-method is supported by the commercial tool *Atelier*  $B^5$  from ClearSy, a French company. Event-B is supported by the open-source tool *Rodin*<sup>6</sup>. Furthermore, an extension *ProB* provides model checking and animation to Event-B specifications [96].

#### 1.2.3 Alloy

Alloy [57] is a declarative formal specification language for describing software abstractions; it was developed to adapt a declarative language like Z to bring in fully automatic analysis. At the core, Alloy is based on relations over atoms with a logic that is small, simple and expressive. It is based on a relational logic that combines the quantifiers of first-order logic with operators of relational calculus. It is easy to learn and understand if one already is familiar with basic set theory. The Alloy language is more than just logic; it provides

<sup>&</sup>lt;sup>2</sup> http://czt.sourceforge.net

<sup>&</sup>lt;sup>3</sup> http://www.deploy-project.eu/

<sup>&</sup>lt;sup>4</sup> http://www.advance-ict.eu/

<sup>5</sup> http://www.atelierb.eu/en/

<sup>6</sup> http://sf.net/projects/rodin-b-sharp

ways to organise a model, build larger models based on smaller ones and a way to factor out components for reuse. The language also provides a number of commands needed to communicate with the Alloy Analyzer. And, finally, the language includes modules, polymorphism, parametrized functions etc., though some features are unique to Alloy including *signatures* and the notion of *scope* that is used to describe structure and define the scope of analysis.

#### **Tools for Alloy**

The Alloy Analyzer is a bounded model finder that has proven to be useful for validating specifications in the Alloy language [57]. The analyzer can *find* instances of Alloy specifications, as well as checking user defined assertions. The analyzer can provide immediate visual feedback when an instance is found or present a *core* containing the top level formulas if no instance could be found. The analyzer is built on top of a boolean satisfiability (SAT) solver, which is used to find an instance by converting the Alloy signatures to boolean formulas, and then find an assignment to all variables so these formulas are satisfied.

#### 1.2.4 The Vienna Development Method

The Vienna Development Method (VDM) [10, 61, 62, 31] was originally developed at the IBM laboratories in Vienna in the 1970's and, as such, it is one of the longest established formal methods. The VDM Specification Language is a language with a formally defined syntax, and both static and dynamic semantics [119, 81]. Models in VDM are based on data type definitions built from simple abstract types using booleans, natural numbers, characters and type constructors for product, union, map, (finite) set and sequences. Type membership may be restricted by predicate invariants meaning that run-time type checking is also required from an interpreter perspective. Persistent state is defined by means of typed variables, again restricted by invariants. Operations that may modify the state can be defined implicitly, using standard pre- and post-condition predicates, or explicitly, using imperative statements. Such operations denote relations between inputs, outputs and states before and after execution; note that such relations allow nondeterministic behaviour. Functions are defined in a similar way to operations, but may not refer to state variables. Recursive functions can have a measure defined for them to ensure termination [124]. Arguments passed to functions and operations are always passed by value, apart from object references.

Three different dialects exist for VDM: The ISO standard VDM Specification Language (VDM-SL) [32], the object oriented extension VDM++ [33] and a further extension of that called VDM Real Time (VDM-RT) [146, 52].

None of these dialects are generally executable since the languages permit the use of type bindings with infinite domains, or implicitly defined functions and operations, but the dialects all have subsets that can be interpreted [77]. In addition, some commonly used implicit definitions can be executed in principle [42]. A full description of the executable subset of the language can be found in [80].

The dialects VDM++ and VDM-RT allow concurrent *threads* to be defined. Such threads are synchronised using *permission predicates* that are associated with any operation that limits their allowed concurrent execution. Where pre-conditions for an operation describe the condition the caller must ensure before calling it, the permission predicate describes the condition that must be satisfied before the operation can be activated, and until that condition is satisfied the operation call is blocked. The permission predicates can refer to instance variables as well as *history counters* which indicate the number of times an operation has been requested, activated or completed for the current object. In VDM-RT, the concurrency modelling can be enhanced by deploying objects on different CPUs with busses connecting the CPUs. Operations called between CPUs can be asynchronous, so that the caller does not wait for the call to complete.

VDM-RT has a special **system** class where the modeller can specify the hardware architecture, including the CPUs and their bus topology; the dialect provides two predefined classes for the purpose, CPU and BUS. CPUs are instantiated with a clock speed and a *scheduling policy*, either *First-Come*, *First-Served* (*FCFS*) or *Fixed Priority* (*FP*). The initial objects defined in the model can then be deployed to the declared CPUs using the CPU's deploy operation. Busses are defined with a transmission speed and a set of CPUs which they connect. Object instances that are not deployed to a specific CPU (and not created by an object that is deployed), are automatically deployed onto a *virtual* CPU. The virtual CPU is connected to all real CPUs through a *virtual* BUS. Virtual components are used to simulate the external environment for the model of the system being developed.

The semantics of VDM-RT has been extended with the concept of discrete time, so that all computations a thread performs take time, including the transmission of messages over a bus. Time delays can be explicitly specified by special **duration** and **cycles** statements, allowing the modeller to explicitly state that a statement or block consumes a known amount of time. This can be specified as a number of nanoseconds or a number of CPU cycles of the CPU on which the statement is evaluated. All virtual resources are infinitely fast: calculation can be performed instantaneously consuming no time, though if an explicit duration statement is evaluated on a virtual CPU, the system time will be incremented by the duration.

#### **Tools for VDM**

Early tools for VDM, such as Adelard's SpecBox [127] were largely confined to basic static checking and pretty-printing of specifications. Currently, only two tools for VDM are actively maintained, VDMTools [28, 35] and Overture [P74].

VDMTools [35] originated with the Danish company IFAD, but is now maintained and further developed by the Japanese corporation SCSK Systems Inc. This is a closed-source product which includes syntax- and type-checking facilities, an interpreter to support testing and debugging of models, test coverage, proof obligation generators that produce formal specifications of integrity checks that cannot be performed statically, and code generators for C++ and Java. A CORBA-based Application Programmer Interface (API) allows specifications to be executed on the interpreter, but accessed through a graphical user interface, so that domain experts unfamiliar with the specification language can explore the behaviour described by the model by playing out scenarios or other test cases. The interpreter has a dynamic link library feature allowing external modules to be incorporated. VDMTools supports round-trip engineering of VDM++ specifications to UML class diagrams.

A newer tool that is under active development is the Overture tool [P74], described in detail in Section 2.1. It has the advantage over VDMTools that it is open-source and designed to be highly extensible; therefore it provides a good platform for research. The Overture project is a community-based initiative<sup>7</sup> that this PhD project is very much involved with, and many of the contributions in this PhD thesis are associated with different aspects of Overture.

#### 1.3 Modelling of Physical Systems

The modelling and analysis of real system phenomena that one would like to control typically spans multiple disciplines. Models use representations of the various logical and physical laws of a subject system, however, logical

<sup>&</sup>lt;sup>7</sup> Overture: www.overturetool.org

and physical laws use different mathematical frameworks to create useful specifications. The underlying mathematics of physical laws is usually described using differential equations, resulting in Continuous Time (CT) specifications whereas logical laws and computational specifications are usually represented using discrete mathematics in Discrete Event (DE) models. The latter is described in languages as in Section 1.2 and may be interpreted.

The CT languages can be simulated by integrating the differential equations that embodies the specification and provide values of the derivatives at any particular point in time. The term used to describe the tools which perform simulation of such differential equations is called a numerical solver; they simulate by integrating the equations in time steps. A number of different integration methods exist which primarily differ on how they calculate the size of the step, and can generally be divided into two groups: fixed step and variable step.

The fixed step methods always take a predefined step in time without taking into account the dynamics of the system. This is also known as sampling in the computer science domain. The accuracy of the method depends on the step size; the smaller the step size the more accurate the solution is, but the penalty is a slower simulation. Variable step methods use the dynamics of the system to determine how large the step size can be so that a certain accuracy is guaranteed. The advantage is that, usually, fewer steps have to be taken over the full time range. Only at points where the dynamics of the system dictate a certain accuracy, step sizes are decreased. The disadvantage is that it is not possible to know in advance what the next output time will be. Only a maximum step-size can be specified within the integration method, but this maximum is only used if the dynamics of the physical system allow it. Various simulation tools exists of which MathLab<sup>8</sup> Simulink<sup>9</sup> is probably the best known tool. In the Design Support and Tooling for Embedded Control Software (DESTECS)<sup>10</sup> [12, 34] an FP7 research project an alternative tools named 20-sim<sup>11</sup> [14] is used which provides some features similar to that of the MathLab Simulink combination. The DESTECS project provides guidelines and tools for modelling embedded software [116, 115]; the project uses a co-simulation approach that combines a discrete-event formalism, like all the formalisms presented in Section 1.2, with CT formalisms.

<sup>&</sup>lt;sup>8</sup> MathLab: http://www.mathworks.com/products/matlab

<sup>9</sup> Simulink: http://www.mathworks.com/products/simulink

<sup>&</sup>lt;sup>10</sup> DESTECS: http://destecs.org

<sup>&</sup>lt;sup>11</sup> 20-Sim: http://www.20sim.com

The project also focuses on how faults can be modelled in such multi-domain systems [117].

#### 1.4 Motivation

The adoption of formal methods, and the underlying specifications languages, by industry is highly dependent on available tool support since it affects risk and cost during development [50]. While not all believe that tools are needed as in [19] where it is mentioned that tools are neither necessary nor sufficient for an efficient formal method application. However, the survey [157] states that it is almost inconceivable that an industrial application would proceed without tools. It is also reported that the tools investigated in the survey are not felt in general to be of sufficient quality for wide-scale applications. These tools must also be available to various platforms, and integrated with features that allow for version control and co-operative development. In [153, 66, 152] the authors suggest that integration of tooling for formal methods into existing development tools may improve the industrial adoption. A key factor for the application of formal methods is that automation is capable of reducing otherwise time consuming tasks while still being flexible [153]. A successful example of how one person-month is reduced to 17 minutes of computation illustrates how automation is able to drastically reduce the time spent performing analysis of specifications [129]. Thus the overall motivation behind this PhD project is to attempt to improve the tool automation of the VDM formal method enabling more widespread industrial take up.

#### 1.5 Research Method

The approach that was taken in this PhD project focused on how the analysis of VDM specifications could be enhanced to automate procedures that otherwise would be manual.

The method followed was based on the identification of areas where the existing support was not yet automated or capable of performing analysis. The work was driven by a number of external industrial case studies from the DESTECS project: a self-balancing scooter, a document inserting system and a dredging excavator [13].

These case studies led to the discovery of a number of limitations of the ability to either express or analyse parts of the case studies with respect to the objectives set for this PhD project. These limitations led to the identification

of contributions that could make it possible to model and perform analysis of the case studies. The contributions that were identified range from the ability to deterministically simulate discrete-event systems but also included the ability to describe and simulate systems that require high-fidelity environment representations. Other contributions focused more on the development of the discrete-event systems and understanding and communication of its behaviour.

Whenever a limitation was identified, the existing literature was searched for similar problems and corresponding solutions. If a solution was found it was adapted and extended to fit the needs, or otherwise a new theoretical solution was constructed. These were, in most cases, followed by a proof of concept implementation of the theory, and evaluation of the support on concrete VDM specifications, including the case studies. Depending on the outcome, theories were adjusted, and the prototype was improved. When a solution that could be considered as a new contribution was reached, it was reported in the form of publications to either workshops, conferences or journals.

#### 1.6 Research Objectives

The thesis objective is to increase the applicability of existing analysis techniques for formal methods-based models, in particular those based on industrial cases and those that involve a higher degree of complexity than the usual textbook case studies. As complex specifications are often modelled using multiple tools and notations, this thesis also investigates the connections that are possible between the multiple notations used in these models.

Given that a formal method approach results in software with fewer faults, the hypothesis is that a higher degree of automated analysis will allow formal methods-based approaches to be a viable alternative for software development to the traditional approaches used in industry.

To accomplish this, it is necessary to enhance the fidelity of formal specifications in relation to the final system's environment, and also to improve and extend the analysis already available within the scope of validation and translation, while maintaining a formal semantic foundation. VDM is used throughout this work as the base formal method, and it has been shown elsewhere to be a suitable formal method for industrial applications [157, 76].

#### 1.7 Evaluation Criteria

The developed automation has been evaluated with regards to the properties described below. The properties are defined primarily based on the industrial statements about tool requirements described in Section 1.4, and the industrial case studies from the DESTECS project.

The individual contributions made in this PhD project are numbered explicitly in Chapter 2 and 3. There is a total of 16 contributions, each of which have been evaluated using the following criteria:

- **Semantic foundation:** The languages that automated analysis are developed for must have a well defined semantic foundation.

- Language completeness: The analysis of a specification must cover the complete specification language either in the form of a single type of analysis or by combining different types of analysis. Likewise, any limitations must be clearly identified.

- **Reduction of manual labour:** The workload of the user must be reduced by automated analysis; this includes reduction of the required user guidance for any particular kind of analysis.

- **Fidelity of embedded control systems:** To describe and perform analysis on specifications of embedded control systems that rely heavily on high-fidelity representations of the target physical environment; it is required that support is available for modelling of both the embedded system as well as the environment.

- **Integration with other tools:** Integration between tools supporting different languages is important if it brings value to the different stakeholders or improves the communication between stakeholders. Therefore, a translation should be enabled if the desired view or analysis already has tool support in another language.

The evaluation of the contributions is described in Section 4.3 where the level of fulfilment of all contributions are compared to each criteria. The comparison is illustrated using a chart as shown in Figure 1.1; the covered area indicates to what extent the criteria are fulfilled. The chart can be used to see the relation between contributions and fulfilment of criteria.

The contributions are motivated by the external industrial case studies and have been posed as a solution to the objectives but are not generalizable

Figure 1.1: Example comparison chart.

for every possible application. However, the contributions have been incorporated into tools used by the industrial partners that enabled them to carry out their case studies with success.

#### **1.8 Published Work**

This section presents the work published during this PhD project, it mainly focuses on the topics *tool automation*, and the formal *semantics* of VDM.

#### 1.8.1 Publications

The publications listed here are all included in this thesis in Part II.

- [P74] Peter Gorm Larsen, Nick Battle, Miguel Ferreira, John Fitzgerald, Kenneth Lausdahl, and Marcel Verhoef. *The Overture Initiative – Integrating Tools for VDM*. SIGSOFT Softw. Eng. Notes, 35(1):1–6, January 2010.

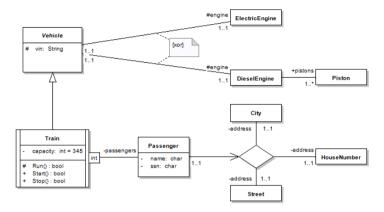

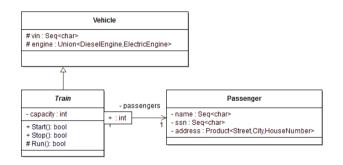

- [P89] Kenneth Lausdahl, Hans Kristian Agerlund Lintrup, and Peter Gorm Larsen. Connecting UML and VDM++ with Open Tool Support. In Ana Cavalcanti and Dennis R. Dams, editors, Proceedings of the 2nd World Congress on Formal Methods, volume 5850 of Lecture Notes in Computer Science, pages 563–578, November 2009. Springer-Verlag. ISBN 978-3-642-05088-6.

- [P83] Kenneth Lausdahl. Translating VDM to Alloy. In Einar Broch Johnsen and Luigia Petre, editors, Integrated Formal Methods, volume 7940 of Lecture Notes in Computer Science, pages 46–60. Springer Berlin Heidelberg, 2013. 10th International Conference, IFM 2013.

- [P87] Kenneth Lausdahl, Peter Gorm Larsen, and Nick Battle. A Deterministic Interpreter Simulating a Distributed Real Time System using VDM. In Shengchao Qin and Zongyan Qiu, editors, Formal Methods and Software Engineering, volume 6991 of Lecture Notes in Computer Science, pages 179–194, 2011. Springer-Verlag. ISBN 978-3-642-24558-9.

- [P79] Peter Gorm Larsen, Kenneth Lausdahl, and Nick Battle. Combinatorial Testing for VDM. In Proceedings of the 2010 8th IEEE International Conference on Software Engineering and Formal Methods, SEFM'10, pages 278–285, Washington, DC, USA, September 2010. IEEE Computer Society. ISBN 978-0-7695-4153-2.

- [P107] Claus Ballegaard Nielsen, Kenneth Lausdahl, and Peter Gorm Larsen. *Combining VDM with Executable Code*. In John Derrick, John Fitzgerald, Stefania Gnesi, Sarfraz Khurshid, Michael Leuschel, Steve Reeves, and Elvinia Riccobene, editors, Abstract State Machines, Alloy, B, VDM, and Z, volume 7316 of Lecture Notes in Computer Science, pages 266– 279, 2012. Springer-Verlag. ISBN 978-3-642- 30884-0.

- [P125] Augusto Ribeiro, Kenneth Lausdahl, and Peter Gorm Larsen. Run-Time Validation of Timing Constraints for VDM-RT Models. In Sune Wolff and John Fitzgerald, editors, Proceedings of the 9th Overture Workshop, number ECE-TT-2 in Technical Report Series, pages 4–16, June 2011.

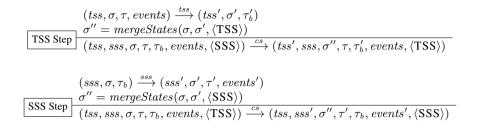

- [P86] Kenneth Lausdahl, Joey W. Coleman, and Peter Gorm Larsen. *The Execution Semantics of VDM Real-Time in a Co-Simulation Environment*. Submitted for publication to the International Journal on Software Tools for Technology Transfer, June 2013.

- [P18] Joey W. Coleman, Kenneth Lausdahl, and Peter Gorm Larsen. Semantics for Generic Co-simulation of Heterogenous Models. Submitted for publication to the Formal Aspects of Computing journal, April 2013.

#### 1.8.2 Other Publications

The publications listed here have not been selected for inclusion in this thesis but are all available from the respective publishers.

[P75] Peter Gorm Larsen, Nick Battle, Miguel Ferreira, John Fitzgerald, Kenneth Lausdahl, and Marcel Verhoef. *The Overture Initiative – Integrat-*

*ing Tools for VDM*. In Min Zhang and Volker Stolz, editors, Harnessing Theories for Tool Support in Software, pages 9–19, November 2010.

- [P108] Claus Ballegaard Nielsen, Kenneth Lausdahl, and Peter Gorm Larsen. Using the Overture Tool as a More General Platform. In Franco Mazzanti, editor, iFM 2012 & ABZ 2012 - Proceedings of the Posters & Tool demos Session, pages 1–34. CNR-ISTI, June 2012.

- [P90] Kenneth Lausdahl and Augusto Ribeiro. Automated Exploration of Alternative System Architectures with VDM-RT. In Sune Wolff and John Fitzgerald, editors, Proceedings of the 9th Overture Workshop, number ECE-TT-2 in Technical Report Series, pages 17–31, June 2011.

- [P125] Augusto Ribeiro, Kenneth Lausdahl, and Peter Gorm Larsen. Run-Time Validation of Timing Constraints for VDM-RT Models. In Sune Wolff and John Fitzgerald, editors, Proceedings of the 9th Overture Workshop, number ECE-TT-2 in Technical Report Series, pages 4–16, June 2011.

- [P91] Kenneth Lausdahl, Marcel Verhoef, Peter Gorm Larsen, and Sune Wolff. Overview of VDM-RT Constructs and Semantic Issues. In Ken Pierce, Nico Plat, and Sune Wolff, editors, Proceedings of the 8th Overture Workshop, number CS-TR-1224 in Technical Report Series, pages 57–67, September 2010.

- [P85] Kenneth Lausdahl, Joey W. Coleman, and Peter Gorm Larsen. Semantics of the VDM Real-Time Dialect. Technical Report ECE-TR-13, Aarhus University, April 2013.

- [P84] Kenneth Lausdahl, Joey W. Coleman, and Peter Gorm Larsen. *Towards a Co-simulation Semantics of VDM-RT/Overture and 20-sim.* In Nico Plat, Claus Ballegaard Nielsen, and Steve Riddle, editors, Proceedings of the 10th Overture Workshop, number CS-TR-1345 in Technical Report Series, pages 30–37. Computing Science, Newcastle University, August 2012.

In addition to the above listed publications, a new book is being prepared as a follow-up to the DESTECS project. The author of this PhD thesis will also contribute as co-author of chapters based on tool usage and the semantics of the co-simulation that forms part of this PhD project. Finally, the author of this PhD thesis has been co-author of [P128, P155], but these publications are not related to the research conducted in this PhD project.

#### 1.9 Outline and Reading Guide

This thesis is structured in two parts. Part I, gives an overview of the contributions based on a selection of the publications carried out as part of this PhD project. Contributions are numbered e.g. [C1], and framed. Part II, contains a selected subset of the actual publications that is the base of the contributions; all publications in this part start with a description about where the paper was published followed by the paper as published.

The publications introduced in Part I all fall within the topic of "*Enhancing Formal Modelling Tool Support with Increased Automation*". The purpose of this part is to give an overview of the publications while introducing relevant background material and related work. Part I introduces a total of 15 publications. To make it possible to distinguish these publications from other references, they are prefixed with "P" e.g. [P89].

Part I is structured as follows; after the introduction in this chapter, Chapter 2 presents the publications: [P74, P75, P108, P89, P83, P87, P107, P79, P90, P125] all concentrating on *Tool Automation*. The chapter starts by giving some background about the context in which the work has been carried out, followed by a description of the work related to tool automation. The contributions described in this chapter primarily focuses on tool aspects of validation. This includes both interpretation of discrete-event systems and reactive control systems that require high-fidelity representation of the environment.

Chapter 3 introduces the *Semantics* work that the tool automation is based upon with focus on the new semantics for VDM-RT and a co-simulation framework. This chapter is based on the publications: [P91, P85, P86, P84, P18]. Finally, Chapter 4 concludes and discusses the contributions<sup>12</sup> from Chapter 2 and 3, and how they relate to each other and fulfil the objectives from Section 1.6.

Part II lists a selection of papers that is written by the author of this PhD thesis or in collaboration with others. Each chapter presents one or two publications and starts by listing the bibliography entry for the publication used throughout this thesis followed by the publication in its original published form.

<sup>&</sup>lt;sup>12</sup> The electronic version of this thesis uses hyper-links to link each contribution reference to its definition.

# 2

## **Tool Automation**

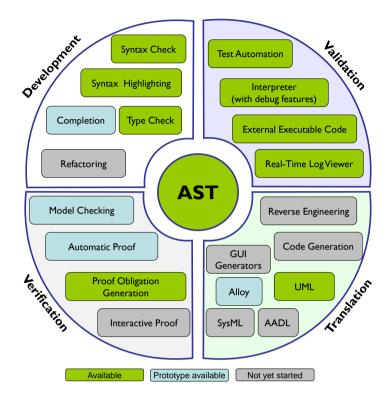

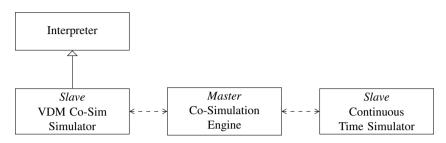

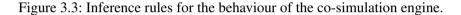

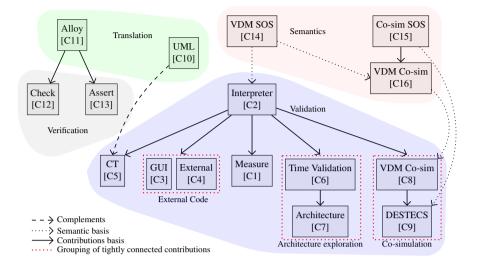

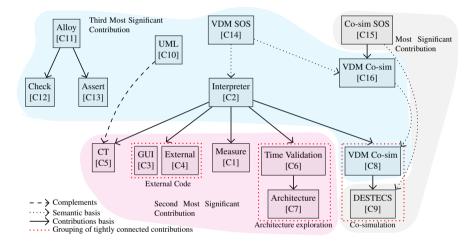

This chapter explains how the Overture tool has developed over time and how this PhD project has been involved in the development of many of the current features and how it influenced the development of the internal architecture. The current status of the Overture features is shown in Figure 2.1 which groups the features into four groups: (1) The *development* group includes basic features needed for a Integrated Development Environment (IDE), (2) The *validation* group includes different feature all related to interpretation, (3) The *translation* group includes different translators for other modelling or programming languages, (4) The *verification* group includes features for model checking or proving properties about VDM models. The work carried out during this PhD thesis is mainly focused on the three first groups where work has been done in the development group to create a framework to support the research carried out in the verification and translation groups.

#### 2.1 Overture in a Historical Perspective

The Overture open source initiative was started in 2003 by the authors of [33]. From the beginning, the mission of the Overture project was defined as:

- To provide an industrial-strength tool that supports the use of precise abstract models in any VDM dialect for software development.

- To foster an environment that allows researchers and other interested parties to experiment with modifications and extensions to the tool and the different VDM dialects.

In the first years of the Overture project, work was solely performed by MSc students starting with [142, 143] with a focus on using XML as the internal data structure. This was followed by [109] where the Abstract Syntax Tree (AST) was manually implemented resulting in numerous bugs. As a reaction

#### 20 2 Tool Automation

Figure 2.1: Overture Overview

to this Marcel Verhoef suggested a way to automate the classes for the underlying AST by producing a tool called ASTGen. A key feature of ASTGen was the ability to automatically generate both the java code implementing the different nodes in the AST. This is to be used inside the Eclipse integrated development environment for the implementation of the Overture tool and in addition a possibility to generate the corresponding AST at a VDM level.

The AST representation at the VDM level was desirable in order to enable development of core components using VDM itself in the same kind of boot-strapping fashion that was successfully applied in the development of VDM-Tools [73]. This approach has been used in the following MSc projects: static semantics [16], proof support using HOL [149], connection to JML [151], test automation [131] and coupling to UML2.0 [88].

In parallel with these efforts a stand-alone command-based tool called VDMJ was developed by Nick Battle [8]. An attempt to build a common

Overture front-end using Eclipse was then made in [104]. This naturally also meant that basic conversions between the AST generated using ASTGen and the AST inside VDMJ was needed.

The Eclipse front-end was then subsequently significantly improved and extended with full interpretation and debug capability using VDMJ. Furthermore, both the Eclipse front-end and VDMJ were updated to enable the DESTECS project to use Overture as its platform.

During 2012 the development of Overture struggled with an ever increasing effort required to maintain the multiple ASTs used by the various features. Therefore, a new attempt was made to create a new common AST that could meet the analysis requirements of all existing features of Overture but at the same time make it flexible and extensible to prepare for new features. It was decided to create a tool that could generate the AST and visitors supporting any analysis code needed.

The new tool AST-Creator, inspired by ASTGen, was developed enabling the automatic generation of a new common Overture AST based on the VDMJ internal structure. This new tool was developed to create a new AST for Overture with improved analysis features for e.g. translators. This included a new feature with ability to extend the Overture AST in a way that allowed reuse of all existing features. The Overture front-end and VDMJ were converted to use the new AST in the period between summer 2012 to spring 2013. As a part of this PhD project, a version of the coupling to UML [P89] and a new translator for VDM to Alloy [P83] were developed using the new analysis feature after the successful conversion of Overture.

Pre-dating this PhD thesis and the DESTECS project, we published a vision paper about the Overture tools for VDM [P74] describing the then current status and further plans for the Overture community. That then later was followed-up by a number of tool automation papers [P78, P75, P108] published during this PhD project to make others aware of the active research on tools for VDM.

#### 2.2 Development

The Overture platform was chosen as the basic research platform for this PhD project. Before this PhD project, a number of features were developed independently of each other, and as a result, a number of different ASTs for the VDM language were used internally. During this PhD project, features were upgraded to make use of the same AST, and thus allowing a better integration; this resulted in a modern IDE that both includes editing capabilities as well as

#### 22 2 Tool Automation

different kinds of analysis for the VDM language. Most of the work carried out during this development did not lead to any direct publications; the most important contribution was the influence on the design of the internal AST for which a new language and generator was developed. This new generator was used to solve the issue with multiple ASTs [82], and at the same time make it easier to implement various kinds of analysis e.g. type check, translations for UML and Alloy. The outcome of this development effort have been a new IDE that is designed with extensibility in mind that was able to serve as a platform for the rest of the work described in this chapter.

#### 2.3 Validation

Validation of specifications can be carried out in a number of different ways e.g. manual inspection, proof of properties of the system or execution. This section describes various contributions related to the execution of VDM specifications. It can be useful for the user to demonstrate the behaviour of a specification before implementation costs are accumulated [43, 72, 46]. This gives the user hands-on experience early in the specification process. In [48] they suggest that this leads to over-specification of systems, and that only system properties should be recorded so that one does not exclude any possible valid implementations. However, others [43, 72] argue that only minimal design decisions are needed to make specifications executable. This makes validation through execution a cost-effective supplement to e.g. proofs [46].

The VDM language is generally non-executable but it contains a subset that can be executed [77], earlier work has also been carried out to extend the executable subset with implicit function and operations [42]. In this section we present a way to interpret VDM specifications, improve test generation through automation and how to improve analysis and the representation of embedded systems using VDM-RT. We also show how a specification can be graphically visualized and integrated with existing code.

#### 2.3.1 Interpretation

Simulation of a system is an easy way to gain knowledge about design options before any formal analysis is carried out. One way to efficiently find problems with a formal model is to evaluate expressions using the definitions of the model. In the event that such expressions do not yield the expected values, it is essential to be able to deterministically reproduce the problem, for example by debugging the model using a deterministic interpreter. The VDM language contains looseness that allows the modeller to gain abstraction and to avoid implementation bias; to perform simulation, tool support must provide an interpreter and debugging environment that allows the designer to investigate and reproduce problems; as a result the interpreter must be able to deal with looseness deterministically both during interpretation and debugging, otherwise it may not be possible to reproduce problems.

In [P87] we presented a deterministic interpreter and debugger that supports all VDM dialects. The interpreter is based on the semantics given in [146, 52, 145] and is able to interpret the executable subset of the different VDM dialects including looseness [77] and non-determinism. A specification that contains looseness may have many semantic models but validation through interpretation only selects a single model that can be executed at the time. As a result, only a single semantic model is executed leaving the rest unexplored.

Validation of specifications is not a new approach but has been done by others like VDMTools [77] from which this work was mainly inspired. The ProB tool [95] for the B language focuses on execution of implicit definitions. The ProB tool has also been used for Z specifications [118]; none of the other interpreters/translators to programming languages of the Z notation [23, 141, 11, 132] include the notion of concurrency as presented in our work. The POOSL approach has significant similarities with VDM-RT and as opposed to the other tools for B and Z includes the ability to describe distributed systems [140, 38]; they resolved non-determinism by always selecting the first option when a finite collection of possibilities exist but they do not have the interactive debugging functionality as described in our work. Our work differs from previous work by mainly focusing on the deterministic execution/debugging of distributed and concurrent systems, and the support for run-time termination check of recursive functions.

This section is outlined with a description of the sequential interpretation of VDM in Section 2.3.1.1, followed by the concurrent interpretation in Section 2.3.1.2 and finished with Section 2.3.1.3 about combining the interpreter with external executable code.

#### 2.3.1.1 Interpreting Sequential Models

The interpretation of sequential specifications starts out by converting the definitions from the model into their semantic equivalent; this is achieved by a tree traversal. The VDM language was not designed for interpretation and therefore the process of this transformation can be complex because of the potential dependencies between definitions. The interpreter operates with specific values and not symbolic values, and therefore the initialization

of a specification amounts to the evaluation of the state, either in VDM-SL state definitions or in VDM++ or VDM-RT static class definitions. The initialization is guided by the definition dependency ordering and deterministically initializes definitions that do not have an explicit ordering; as a result a re-initialization always produces the same initial state.

The execution of a function or operation in the interpreter is in the simplest case carried out by evaluation of the argument expressions followed by the body of the function or operation. However, the interpreter is also capable of checking pre- and post-conditions, type and state invariants, recursive measures and perform general runtime type checking during execution. The complete execution order is as follows:

- 1. Type check function arguments

- 2. Check function pre-condition

- 3. Check measure if defined

- 4. Evaluate function body

- 5. Type check function result

- 6. Check function post-condition

The new addition here is the measure check that checks for termination in case of a recursive function. The measure check uses a special measure function [124] that must be defined; this function takes the same arguments as the recursive function it is a measure of but must have a return type of  $\mathbb{N}$ . The measure must be defined in terms of its arguments so that it is strictly decreasing for every nested call in the recursion function<sup>1</sup>.

Looseness in VDM can be illustrated by e.g. the let-be expression, the expression represents a choice as shown in let a in set  $\{1, 2\}$  in a where this expression denotes either 1 or 2. This is deliberately left as an implementation choice from a refinement perspective. To interpret such models the interpreter chooses one of the possible semantic models. In order for the interpreter to produce executions, it must choose one of the possible semantic models in order to produce a deterministic interpretation. The iterations over a set of elements poses a similar challenge where the order of the set must be the same for every execution. As a result, this interpreter can deterministically execute sequential models containing looseness and therefore it is easy to

<sup>&</sup>lt;sup>1</sup> Note there are still cases where it is impossible to express a measure functions i.e. directly over tree structures

reproduce any problems discovered during execution for later inspection. The interpreter only selects a single semantic model to execute for performance reasons; it is theoretically possible to calculate all semantic models from an executable specification as described in [71].

**Contribution 1.** Run-time termination checks of recursive functions using measure functions.

### 2.3.1.2 Interpreting Concurrent Real-Time models

Interpretation of concurrent and concurrent real-time systems is in itself not new, and has been done in e.g. LOTOS [55] with CSP [51] and CSS [102] and TCOZ [97] for Timed CSP [123]. However, the VDM language differs from CSP and Timed CSP by using a state based approach alternative to the algebraic approach used in CSP. The approach taken in TCOZ is to combine Timed CSP with a state based approach (Object Z). This is to some extent similar to VDM-RT which also includes timing primitives and has support for modelling of multi-threaded concurrency.

The sequential interpretation presented until now only reflects execution of VDM-SL or non-threaded VDM++ specifications and thus results in a single threaded evaluation that always produces the same result because the interpreter treats all loose operations as under-determined rather than non-deterministic [77]. Under-determined denotes the set of all possible deterministic implementations whereas a non-deterministic approach denotes all possible implementations including non-deterministic implementations.

To simulate specifications of real-time systems that include concurrency and distribution the initialization process must be extended with deployment of objects to CPUs and configuration of the system topology that the interpreter must use during the evaluation. The VDM-RT dialect supports a more precise simulation of how a system behaves, not only with respect to concurrency but also how the interpreted execution time influences the model. The VDM-RT dialect is defined in terms of computational resources such as CPUs and busses which each can have maximum a single running thread at a time. The interpreter must use this information and that of the special **system** class to determine whether interprocess communication over a bus is required.

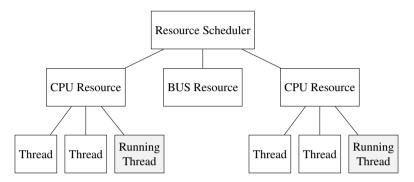

The VDM scheduling is responsible for scheduling resources and the control of the interpreted execution time, and is controlled by a *Resource-Scheduler* that is based on *Resources* as shown in Figure 2.2. A resource is

represented by a separate limited resource in the model, such as a CPU or a bus; A CPU is limited to only run one thread at a time while busses are limited to only communicate one message at a time, this creates a queue of activities per resource. The resource scheduler is responsible for scheduling the execution of resources.

Figure 2.2: Overview of the VDM Resource Scheduler.

To use the same scheduler for simulation of VDM-SL and VDM++ specifications that exclude the notion of time, a special CPU resource (called a virtual CPU) is used and no bus resources are available. The virtual CPU has an infinitely fast simulation time and therefore does not put any timing constraints on the evaluation of the models. Every resource has a scheduling policy which is responsible for determining which thread is the best to run next, and for how long it should be allowed to run (its time-slices).

With VDM-RT, in the event that the active thread is trying to move interpreted execution time, the resource will identify this fact. The resource scheduler is responsible for waiting until *all* resources are in this state, and then finding the minimum time step that would satisfy at least one of the waiting threads. The interpreted execution time is moved forward at this point, and those threads that have their time step satisfied are permitted to continue, while those that need to wait longer remain suspended. This reflects the semantics of VDM-RT as defined in [145, 52] and Chapter 3.

A VDM extract of this behaviour is specified in Listing 2.1. The initial loop establishes whether any resources can progress. The CanProgress operation does a compute step for the resource, if possible. The progressing flag will be **true** if any resource was able to progress. The getTimestep operation either returns the timestep requested by the resource, or **nil**, indicating that it is not currently waiting for time to advance. If no resource

### 2.3 Validation 27

can progress and no resource is waiting for a timestep, the system is *deadlocked*. Otherwise, if no resource can progress and at least one is waiting for a timestep, then system time can advance by the *smallest* requested amount. In this event, every resource is adjusted by the minimum step, which will result in at least one resource being able to progress. This scheduling process continues until the original expression supplied by the user completes its evaluation. Note that the set resources is interpreted here according to the looseness defined in [77] posing a deterministic ordering on the resources.

```

progressing := false;

for all resource in set resources do

-- record if at least one resource is able to progress

progressing := CanProgress(resource) or progressing;

let timesteps =

{resource.getTimestep() | resource in set resources}\{nil}

in

- nobody can progress and nobody is waiting for time

if not progressing and timesteps = {}

then error -- deadlock is detected

-- nobody can progress and somebody is waiting for time

elseif not progressing and timesteps <> {}

then let mintime = Min(timesteps)

in

(SystemClock.advance(mintime);

for all resource in set resources do

AdvanceTime(resource, mintime))

else -- continue scheduling

```

Listing 2.1: Overview of the internal scheduling sequence.

Debugging multi-threaded programs is another challenge not solved by simply using a deterministic interpreter. Non-deterministic behaviour can easily be introduced if a debugger suspends a single thread in a multiple threaded program. This causes non-deterministic scheduling since the suspended thread is excluded from scheduling, thus decreasing the number of threads in the scheduling algorithm. This introduces non-deterministic behaviour during debug which is difficult to repeat, however, this approach is common and both used by the Java debugger in Eclipse and the C# debugger in Visual Studio.

The solution chosen for the VDM interpreter suspends all threads when a breakpoint is reached; this does not in itself ensure deterministic debugging

but the resource scheduler described above has the overall control and thus controls that the overall scheduling order is preserved.

**Contribution 2.** Deterministic interpretation and debugging of distributed and concurrent systems using a deterministic scheduler.

### 2.3.1.3 Combining VDM with Executable Code

Formal methods are generally difficult to comprehend for people who are not already used to them and this poses a challenge when the formal specification must be compared to the users expectations. Furthermore, links between a specification and external subsystems that are not modelled can be unclear.

In [P107] we present work that allows one to build an interactive graphical representation of an executable specification, including the ability to integrate with external code. The work is inspired by previous work in VDMTools [35] that supported a CORBA link [138] and dynamic loading of DLLs [139]. However, both these approaches were challenging to use compared to our solution. The main difference is that we do not require any syntactic changes to the language. The interpretation of the specification is kept consistent by run-time checks of all calls to external code; including checks for pre/post-conditions, invariants and run-time type checking. The integration of external code still allows the user to debug the specification.

The approach for Coloured Petri Nets: Comms/CPN [44] is a standard ML library that augments e.g. DESIGN/CPN with the necessary infrastructure to establish communication between a CPN model and external processes. The Comms/CPN library enables two-way communication between the CPN model and the external process using TCP/IP, by defining generic send and receive-functions which accept a byte stream of data. Encoding/decoding functions have to be implemented to marshal data for transmission. Comms/CPN has the advantage of using TCP/IP which allows heterogeneous clients to interact with the simulator, while the send/receive approach has the weakness of potentially blocking the simulator while waiting for data transmission and it requires the external process to implement some conveying, and mapping of the received data into concrete functionality e.g. an update of a graphical animation. Comms/CPN differs from our solution since they need to define the connection points used for the TCP/IP connections.

The successor of DESIGN/CPN is Access/CPN [154] which provides a Java interface to the CPN simulator and thus provides a simpler higher level interface. Communication is still done through TCP/IP and this still requires

the definition of connection points. Another approach for Event-B, is B-Motion Studio [67] that makes it possible to create visualizations via a visual editor, and it establishes a link to the model using Event-B expressions as gluing code. The key feature is that it allows a for faster creation of graphical representations without the knowledge of graphical programming. Its focus on easy visualization comes at the cost of flexibility, as users who might want to do advanced features, in particular parts of the visualisation, will lack the versatility provided by access to lower-lever graphical programming. To our knowledge there is no possibility of interacting with the model or visualisation through external executable code. The easy visualization provided by B-Motion Studio would be beneficial for VDM; however, it cannot be directly mapped to VDM because of the dynamic construction of objects allowed in VDM. This dynamic construction of objects is handled in our solution, and a solution is provided that integrates with a graphical user interface generator [111, 110] that in-part resembles B-Motion Studio. Additionally, our solution also has an integration with external legacy code, which is not the focus of B-Motion Studio.

**Contribution 3.** A foundation for integration of graphical user interfaces with an interpreter for run-time manipulation of a specifications.

**Contribution 4.** Integration of external code with the interpretation of specifications without changes to the syntax of the formal language, while preserving the internal run-time checks.

# 2.3.2 Automatic Testing of VDM Specifications

Testing can be used to gain confidence in a specification, but to obtain sufficient coverage of even small specifications a significant effort is required by the user. A solution is to use automatic testing that can generate test cases which then can be checked against the specification. However, this limits testing to only consider run-time errors; a test oracle would also be required to test for defects not resulting in run-time errors.

In [P79] we introduce a combinatorial testing tool that is based on earlier work conducted with the TOBIAS tool by the research group led by Yves Ledru [113, 94, 92, 93], and related to recent work conducted on the

generation of test cases from model checkers [5, 112, 126, 39]. Combinatorial testing in VDM involves the automatic generation and execution of large collections of test cases derived from templates provided in the from of trace definitions added to the VDM language. This approach uses regular expressions to describe possible sequences of operation calls and utilises the run-time checks for VDM to determine if a single test sequence yields a valid result. The results are groups into three categories:

- failed if a run-time error occur during the execution of a test sequence, or

- *inconclusive* if the test contains a call to an operation which pre-condition does not hold, which indicates that the generated test was not a valid test for the specification at hand;

- *passed* this indicates that no run-time errors occurred during execution and that the test is correct in relation to the specification.

The number of tests generated though automatic test generation quickly reaches thousands or even millions. Therefore, it is favourable to reduce the test set while keeping them as representative as possible. Two reduction techniques can be applied: (1) A random selection technique, or (2) a shape reduction technique. The shape reduction technique is divided into three types of reductions where the simplest type defines a shape as a sequence of named operation calls, regardless of their argument values. By guaranteeing to retain at least one example of every test shape, the reduced set of tests can claim to be more representative than e.g. a random selection. The two other shape reduction techniques is based on the injection of explicit variable assignments into test sequences. This enables the shape reduction to take variables into consideration in the analysis, either simply by their name and position in the test sequence, or by both considering their name and assigned value. The effect of using the latter two techniques is finer grained shapes that therefore limits the degree of reduction. The following example from [P79] illustrates the syntax, and what effect the reduction techniques have on the number of tests generated:

```

T: let {x,y,-} in set {{1,2,3},{2,3,4}} in

(op1(x, y) | op2(x + y)) | op1(1, 2)

```

This trace expands to 25 tests: each subset produces six pair-matches for x and y, giving 12 pairs; each pair produces a call to op1 and op2, giving 24 tests; lastly, there is one call to op1 on the end, giving a total of 25.

- **Random reduction:** If we ask for a test reduction of 0.01 (i.e. 1% of the original 25), then using a random reduction technique, we would select one test at random the reduction will never select less than one test.

- Simple shape reduction: If we ask for a simple shaped reduction of 1%, we select two tests at random: one is a call to op1, and one is a call to op2. This is because these are the only two shapes in the set of 25, and the reduction guarantees to retain at least one test of each shape.

- Shape reduction with variable names: If we ask for shaped reduction of 1% with variable *names*, we get three tests: two are as with simple shaped reduction, noting that x and y are set, and the third is the op1(1, 2) call which does not involve any variable settings and therefore is now regarded as a different shape.

- Shape reduction with variable values: Lastly, if we ask for shaped reduction of 1% with variable *values*, we get 21 tests: the only tests missing from the original 25 are those which were duplicated because of the presence of 2 and 3 in *both* subsets i.e. there are two ways for the variables to be set to 2 and 3, and each of these produces two tests because of the op1/op2 alternative, so four duplicates are missing from the total, giving 21 tests.

Note that as the specification of shapes becomes more detailed, it is not possible to achieve the requested 1% reduction in the number of tests. This is a natural consequence of the reduction process retaining at least one test of each shape.

It is worthwhile noting that we extended the combinatorial testing in [P79] to also incorporate the execution of operations that start concurrent threads in VDM++ and VDM-RT so that possible deadlock situations can be detected. However, to fully exploit this we need to extend the syntax to include the non-deterministic VDM statement, which in the interpreter simply executes the statements it contains in a non-deterministic order. In a combinatorial testing context, this construct would expand to all possible orderings of the operation calls included.

Many different approaches to test automation based on formal methods exist [24, 45, 114, 49, 144] and our work on combinatorial testing, is based on the work of Ledru [113, 94, 92]. The main difference in our work is the fact that we have extended the VDM dialects with syntax for trace definitions rather than using an external tool. In addition, we have devoted significant

effort to enable the user to work efficiently with combinatorial testing by enhancing the number of test cases that can be handled and by creating a user interface that enables efficient access to the defects discovered.

In earlier work, the performance of combinatorial testing techniques has been criticized [17]. However, in that work test sequencing was not addressed at all, so they could not bring the system under test into a particular state as we can do with the approach presented here. In that respect, from a test sequencing perspective, combinatorial testing is more closely related to model checking [5, 112, 126, 39]. However, model checkers are typically limited by the total number of classes in the system, whereas here we can directly select test scenarios of interest.

**Contribution 5.** Integration of combinatorial testing in the VDM language, including: a) a new test reduction techniques using variable bindings to define new shape reduction types b) a new construct to express parallelism.

# 2.3.3 Using The Real-Time Extensions

The real-time extension in VDM aims to give a user the ability to analyse how the timing behaviour of the specification changes under different deployment configurations. This information can then be used to assist a user in answering some of the common design questions relating to deployment configurations, which may include the following [145]:

- (a) Does the proposed architecture meet the performance requirements of all applications?

- (b) How robust is the chosen architecture with respect to changes in the application or architecture parameters?

- (c) Is it possible to replace components by cheaper, less powerful equivalents to save cost while maintaining the required performance targets?

The interpreter described in Section 2.3.1.2 is able to simulate real-time systems that include distribution but lacks a way to check *time constraints*, and thus leaves the user with no more knowledge than for a regular non-distributed system. Therefore, the analysis of real-time systems must include

timing requirements; a real-time system can only be considered correct if the system reacts with the correct behaviour within a certain time frame.

In previous work [30], a number of *validation conjectures* were introduced to describe the temporal relationship between system-level events that can be observed in an execution trace from a simulation of a VDM-RT model using VDMTools. An example of a conjecture for a car navigation specification is shown in Listing 2.2; it requires that a volume change must be reflected in the display of the navigation system within 35 ms.

```

deadlineMet(#fin(Radio`AdjustVolumeUp),

#fin(MMI`UpdateScreen),

35 ms)

```

Listing 2.2: Time Constrain Example.

The approach taken in [30] using post-analysis of an execution trace limits the analysis to small examples with simple conjectures due to the amount of data required for their evaluation. Validation conjectures are specified using trigger events associated with operations and expressions over instance variables, and may require a *deadline* to be met, a *separation* or *required separation* between calls. A trigger event indicates that the conjecture must be checked when the event occurs. Events can be one of the following: *request, activate* or *finished*; which indicates different stages of the evaluation of operations. The consequence of being able to express conjectures based on instance variables is that it requires all values of instance variables to be stored every time an event included in a trigger occurs during interpretation of a specification.

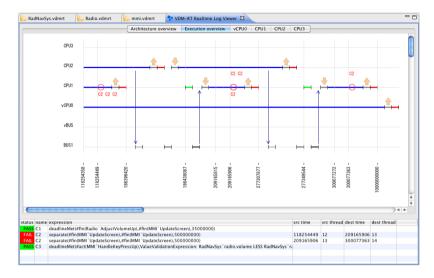

In [P125] we show how conjectures effectively can be checked during simulation by extending the VDM interpreter. This solution only logs the information required to visualize the execution trace, annotated with markers showing where conjectures were violated as illustrated in Figure 2.3. As a result, our solution is more scalable, and it is a good starting point for exploration of alternative architectures. This solution can easily be extended to raise a run-time error when it is detected that the specification does not respect a conjecture and thus mark the system configuration as not acceptable.