**River Publishers Series in Electronic Materials and Devices**

Silicon-Germanium Heterojunction Bipolar Transistors for mm-Wave Systems: Technology, Modeling and Circuit Applications

Niccolò Rinaldi and Michael Schröter (Editors)

# Silicon-Germanium Heterojunction Bipolar Transistors for mm-Wave Systems: Technology, Modeling and Circuit Applications

### **RIVER PUBLISHERS SERIES IN ELECTRONIC MATERIALS AND DEVICES**

Series Editors

EDOARDO CHARBON EPFL Switzerland MIKAEL ÖSTLING KTH Stockholm Sweden

ALBERT WANG

University of California Riverside, USA

Indexing: All books published in this series are submitted to the Web of Science Book Citation Index (BkCI), to CrossRef and to Google Scholar.

The "River Publishers Series in Electronic Materials and Devices" is a series of comprehensive academic and professional books which focus on the theory and applications of advanced electronic materials and devices. The series focuses on topics ranging from the theory, modeling, devices, performance and reliability of electron and ion integrated circuit devices and interconnects, insulators, metals, organic materials, micro-plasmas, semiconductors, quantum-effect structures, vacuum devices, and emerging materials. Applications of devices in biomedical electronics, computation, communications, displays, MEMS, imaging, micro-actuators, nanoelectronics, optoelectronics, photovoltaics, power ICs and micro-sensors are also covered.

Books published in the series include research monographs, edited volumes, handbooks and textbooks. The books provide professionals, researchers, educators, and advanced students in the field with an invaluable insight into the latest research and developments.

Topics covered in the series include, but are by no means restricted to the following:

- · Integrated circuit devices

- Interconnects

- Insulators

- Organic materials

- Semiconductors

- Quantum-effect structures

- · Vacuum devices

- Biomedical electronics

- Displays and imaging

- MEMS

- · Sensors and actuators

- Nanoelectronics

- Optoelectronics

- Photovoltaics

- Power ICs

For a list of other books in this series, visit www.riverpublishers.com

# Silicon-Germanium Heterojunction Bipolar Transistors for mm-Wave Systems: Technology, Modeling and Circuit Applications

**Editors**

### Niccolò Rinaldi

University of Naples Italy

## **Michael Schröter**

Technische Universität Dresden Germany

Published, sold and distributed by: River Publishers Alsbjergvej 10 9260 Gistrup Denmark

River Publishers Lange Geer 44 2611 PW Delft The Netherlands

Tel.: +45369953197 www.riverpublishers.com

ISBN: 978-87-93519-61-9 (Hardback) 978-87-93519-60-2 (Ebook)

©The Editor(s) (if applicable) and The Author(s) 2018. This book is published open access.

#### **Open Access**

This book is distributed under the terms of the Creative Commons Attribution-Non-Commercial 4.0 International License, CC-BY-NC 4.0) (http://creativecommons.org/ licenses/by/4.0/), which permits use, duplication, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, a link is provided to the Creative Commons license and any changes made are indicated. The images or other third party material in this book are included in the work's Creative Commons license, unless indicated otherwise in the credit line; if such material is not included in the work's Creative Commons license and the respective action is not permitted by statutory regulation, users will need to obtain permission from the license holder to duplicate, adapt, or reproduce the material.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper.

## Contents

| Pı | reface              |                                                  | xi    |

|----|---------------------|--------------------------------------------------|-------|

| A  | cknov               | ledgements                                       | XV    |

| Li | st of (             | Contributors                                     | xvii  |

| Li | st of l             | Figures                                          | xix   |

| Li | st of '             | fables                                           | xliii |

| Li | st of A             | Abbreviations                                    | xlv   |

| In | trodu               | ction                                            | 1     |

|    | <i>M</i> . <i>S</i> | chröter                                          |       |

| 1  | SiG                 | e HBT Technology                                 | 11    |

|    | <i>H. R</i>         | ücker and B. Heinemann                           |       |

|    | 1.1                 | Introduction                                     | 11    |

|    | 1.2                 | HBT Performance Factors                          | 13    |

|    | 1.3                 | HBT Device and Process Architectures Explored    |       |

|    |                     | in the DOTSEVEN Project                          | 19    |

|    |                     | 1.3.1 Selective Epitaxial Growth of the Base     | 20    |

|    |                     | 1.3.1.1 DPSA-SEG device architecture             | 21    |

|    |                     | 1.3.1.2 Approaches to overcome limitations       |       |

|    |                     | of the DPSA-SEG architecture                     | 24    |

|    |                     | 1.3.2 Non-selective Epitaxial Growth of the Base | 32    |

|    | 1.4                 | Optimization of the Vertical Doping Profile      | 36    |

|    | 1.5                 | Optimization towards 700 GHz $f_{MAX}$           | 40    |

|    | 1.6                 | Summary                                          | 48    |

|    |                     | References                                       | 49    |

| •   | ~         |

|-----|-----------|

| V1  | Contents  |

| • • | contentis |

| 2 | Devi                | ce Sim   | ulation                                          | 55  |

|---|---------------------|----------|--------------------------------------------------|-----|

|   | <i>M</i> . <i>S</i> | chröter, | G. Wedel, N. Rinaldi and C. Jungemann            |     |

|   | 2.1                 |          | rical Simulation                                 | 55  |

|   |                     | G. Wed   | del and M. Schröter                              |     |

|   | 2.2                 | Device   | e Simulation                                     | 57  |

|   |                     | 2.2.1    | TCAD Davice Optimization                         | 57  |

|   |                     | 2.2.2    | Deterministic BTE Solvers                        | 59  |

|   |                     | 2.2.3    | Drift-diffusion and Hydrodynamic Transport       |     |

|   |                     |          | Models                                           | 64  |

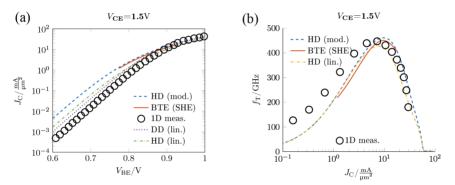

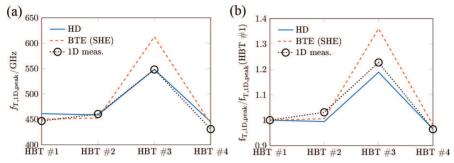

|   |                     | 2.2.4    | Simulation Examples                              | 66  |

|   |                     |          | 2.2.4.1 DD simulation                            | 66  |

|   |                     |          | 2.2.4.2 HD simulation                            | 68  |

|   |                     |          | 2.2.4.3 Effects beyond DD and HD transport       | 71  |

|   |                     |          | 2.2.4.4 Comparison with experimental data        | 82  |

|   | 2.3                 | Advan    | ced Electro-thermal Simulation                   | 85  |

|   |                     | C. Jung  | gemann and N. Rinaldi                            |     |

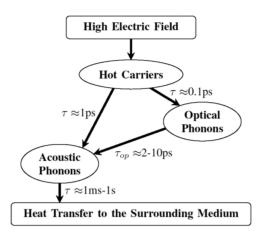

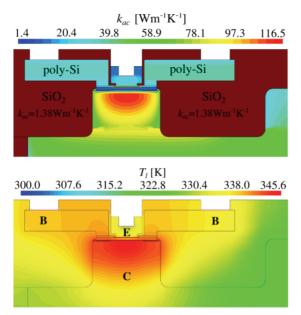

|   |                     | 2.3.1    | Carrier–Phonon System in SiGe HBTs               | 85  |

|   |                     | 2.3.2    | Deterministic and Self-consistent Electrothermal |     |

|   |                     |          | Simulation Approach                              | 87  |

|   |                     | 2.3.3    | Hot Phonon Effects in a Calibrated System        | 89  |

|   |                     | 2.3.4    | Thermal Resistance Extraction from the Simulated |     |

|   |                     |          | DC Characteristics                               | 92  |

|   | 2.4                 |          | scopic Simulation of Hot-carrier Degradation     | 94  |

|   |                     | 2.4.1    | Physics of Hot-carrier Degradation               | 94  |

|   |                     | 2.4.2    | Modeling of Hot-carrier Effects                  | 96  |

|   |                     | 2.4.3    | Simulation of SiGe HBTs under Stress Conditions  |     |

|   |                     |          | Close to the SOA Limit                           | 99  |

|   |                     | Refere   | ences                                            | 105 |

| 3 | SiGe                | e HBT (  | Compact Modeling                                 | 113 |

|   | A. Pa               | awlak, N | M. Schröter and B. Ardouin                       |     |

|   | 3.1                 | Introdu  | uction                                           | 114 |

|   | 3.2                 | Overvi   | iew of HICUM Level 2                             | 116 |

|   | 3.3                 | Model    | ing of the Quasi-Static Transfer Current         | 118 |

|   |                     | 3.3.1    | Basics of the GICCR                              | 118 |

|   |                     | 3.3.2    | SiGe HBT Extensions                              | 121 |

|   |                     | 3.3.3    | Temperature Dependence                           | 129 |

|   | 3.4                 | Charge   | e Storage                                           | 132 |

|---|---------------------|----------|-----------------------------------------------------|-----|

|   |                     | 3.4.1    | Critical Current                                    | 132 |

|   |                     | 3.4.2    | SiGe Heterojunction Barrier                         | 134 |

|   | 3.5                 | Intra-I  | Device Substrate Coupling                           | 136 |

|   | 3.6                 | SiGe H   | HBT Parameter Extraction                            | 140 |

|   |                     | 3.6.1    | Extraction of Series Resistances                    | 141 |

|   |                     | 3.6.2    | Extraction of the Transfer Current Parameters       | 146 |

|   |                     | 3.6.3    | Physics-Based Parameter Scaling                     | 152 |

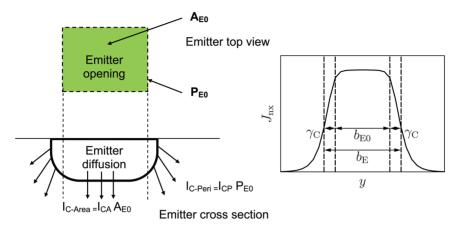

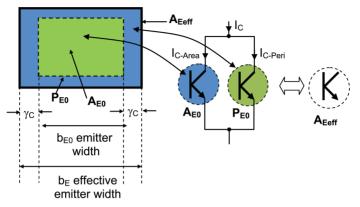

|   |                     |          | 3.6.3.1 Standard geometry scaling equation          | 153 |

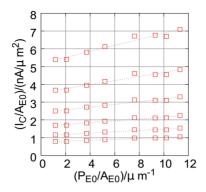

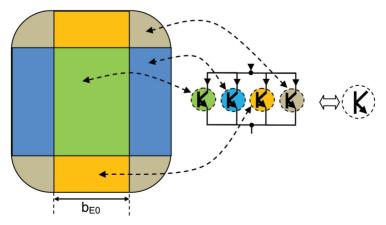

|   |                     |          | 3.6.3.2 Generalized scaling equations               | 155 |

|   | 3.7                 | Compa    | act Model Application to Experimental Data          | 157 |

|   |                     | Refere   | ences                                               | 158 |

| 4 | (Sut                | o)mm-w   | vave Calibration                                    | 163 |

|   | <i>M</i> . <i>S</i> | pirito a | nd L. Galatro                                       |     |

|   | 4.1                 | Introdu  | uction                                              | 163 |

|   | 4.2                 | Multi-   | mode Propagation and Calibration Transfer           |     |

|   |                     | at mm    | -wave                                               | 164 |

|   |                     | 4.2.1    | Parallel Plate Waveguide Mode                       | 165 |

|   |                     | 4.2.2    | Surface Wave Modes: $TM_0$ and $TE_1$               | 165 |

|   |                     | 4.2.3    | Electrically Thin Substrates                        | 167 |

|   |                     | 4.2.4    | Calibration Transfer                                | 168 |

|   | 4.3                 | Direct   | On-wafer Calibration                                | 170 |

|   |                     | 4.3.1    | Characteristic Impedance Extraction of Transmission |     |

|   |                     |          | Lines                                               | 171 |

|   | 4.4                 |          | DUT-plane Calibration                               | 175 |

|   | 4.5                 | Conclu   | usion                                               | 181 |

|   |                     | Refere   | ences                                               | 181 |

| 5 | Reli                | ability  |                                                     | 185 |

|   | <i>V. d'</i>        | Alessan  | dro, C. Maneux, G. G. Fischer, K. Aufinger,         |     |

|   | <i>A. M</i>         | lagnani, | S. Russo and N. Rinaldi                             |     |

|   | 5.1                 | Mixed    | -mode Stress Tests                                  | 185 |

|   |                     | 5.1.1    | Introduction to Hot-Carrier Degradation under       |     |

|   |                     |          | MM Stress                                           | 185 |

|   |                     | 5.1.2    | Long-term MM Stress Characterization                |     |

|   |                     |          | on IHP Devices                                      | 187 |

|   |                     | 5.1.3    | Medium-term MM Stress Characterization              |     |

|   |                     |          | on IFX Devices                                      | 189 |

| viii | Contents  |

|------|-----------|

| ,    | contentio |

|   | 5.2         | Long-t   | term Stress   | s Tests                               | 193 |

|---|-------------|----------|---------------|---------------------------------------|-----|

|   |             | 5.2.1    | Experime      | ental Setup                           | 194 |

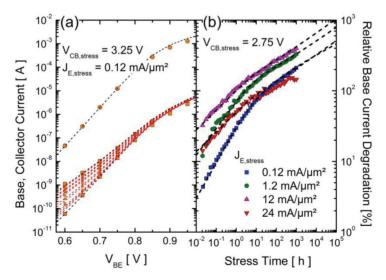

|   |             | 5.2.2    | Long-ter      | m Degradation Test Results            | 195 |

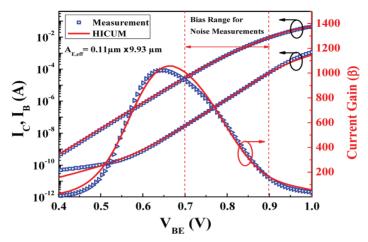

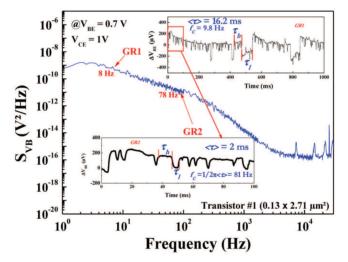

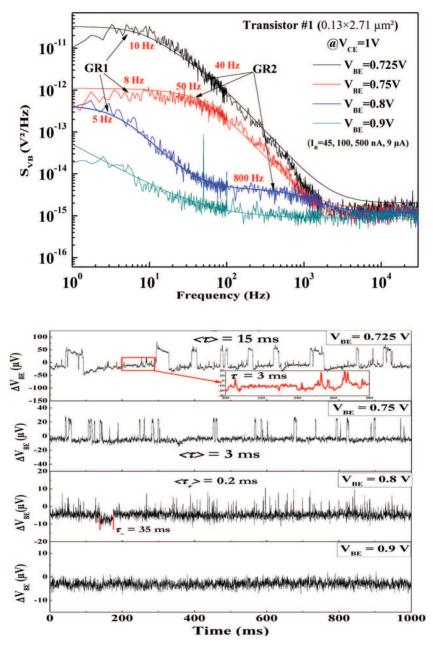

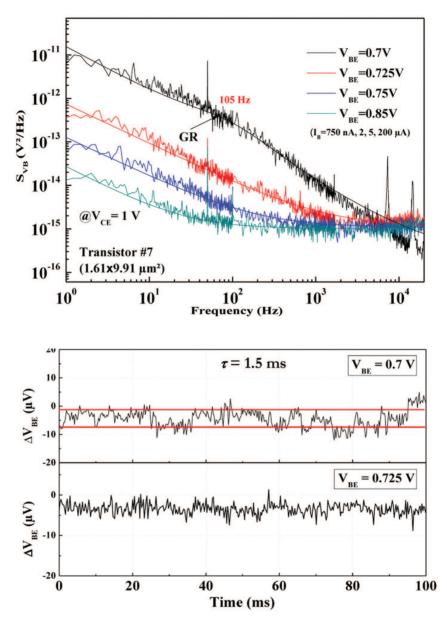

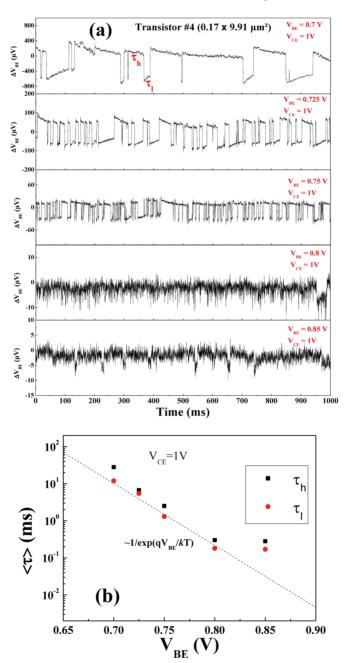

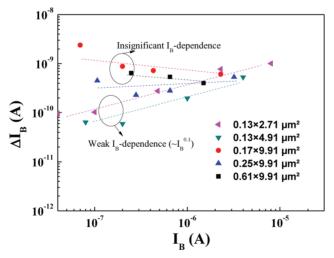

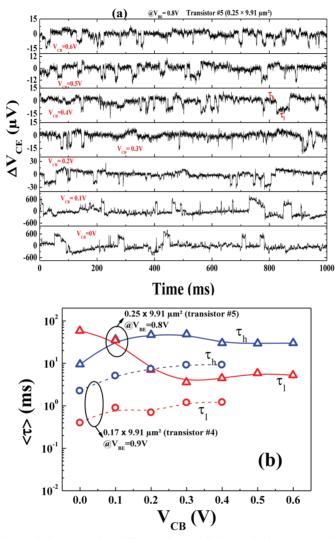

|   |             | 5.2.3    | Low-free      | quency Noise Characterization         | 201 |

|   | 5.3         | Compa    | act Modeli    | ng of Hot-Carrier Degradation         | 210 |

|   |             | 5.3.1    | Empirica      | l Equations by IHP                    | 210 |

|   |             | 5.3.2    | HICUM-        | based Model                           | 212 |

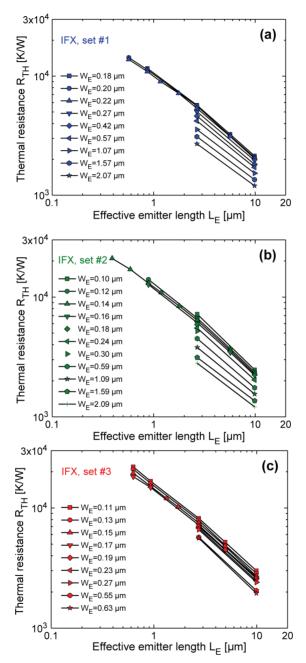

|   | 5.4         | Therm    | al Effects    |                                       | 213 |

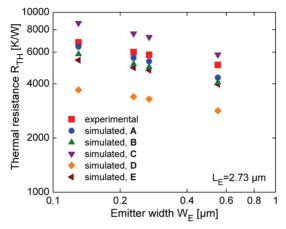

|   |             | 5.4.1    | Experime      | ental $R_{\rm TH}$ Extraction         | 214 |

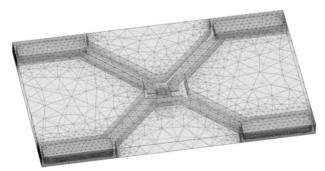

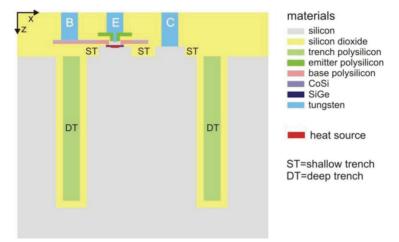

|   |             | 5.4.2    | Thermal       | Simulation                            | 217 |

|   |             | 5.4.3    | Scaling (     | Considerations                        | 224 |

|   |             | Refere   | nces          |                                       | 227 |

| 6 | Mill        | imeter-  | wave Circ     | uits and Applications                 | 235 |

|   | <i>A. M</i> | lukherje | e, W. Lian    | g, M. Schröter, U. Pfeiffer, R. Jain, |     |

|   |             |          | l P. Hillger  | 0 00                                  |     |

|   | 6.1         | Millim   | neter-wave    | Benchmark Circuits and Building       |     |

|   |             | Blocks   | 5             |                                       | 235 |

|   |             | A. Muk   | kherjee, W.   | Liang and M. Schröter                 |     |

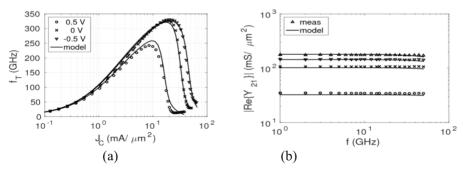

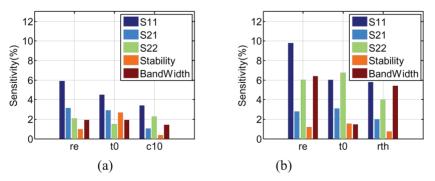

|   |             | 6.1.1    | Benchma       | ark Circuits                          | 236 |

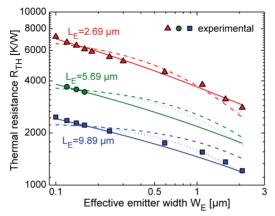

|   |             | 6.1.2    | Circuit B     | Building Blocks                       | 245 |

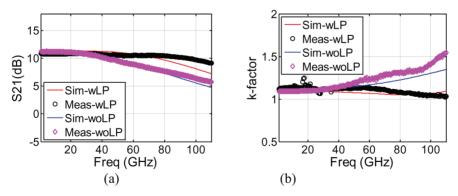

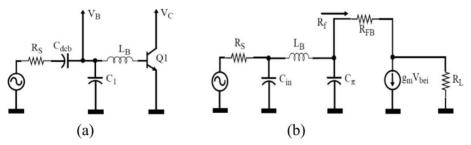

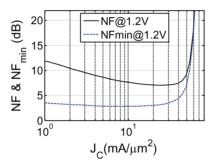

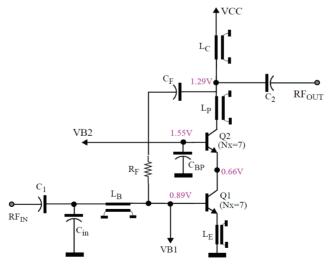

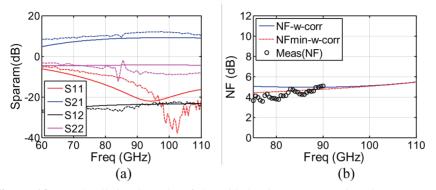

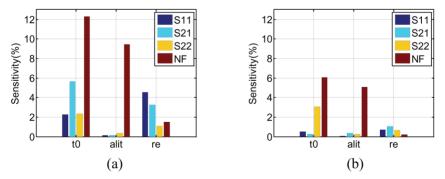

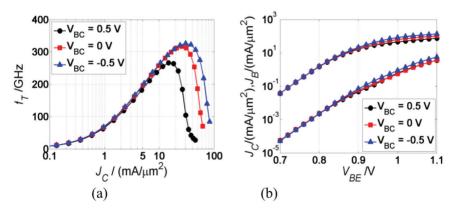

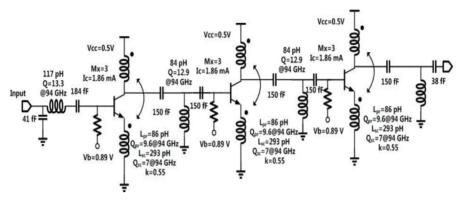

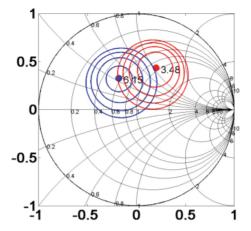

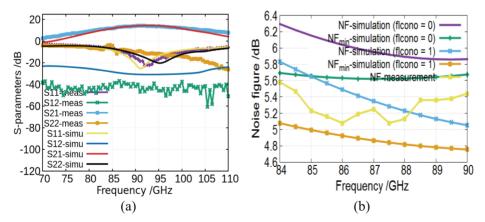

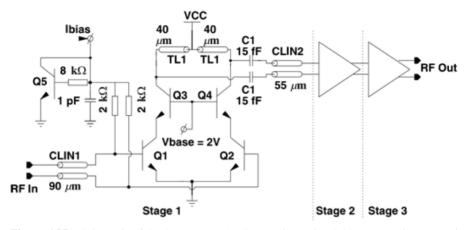

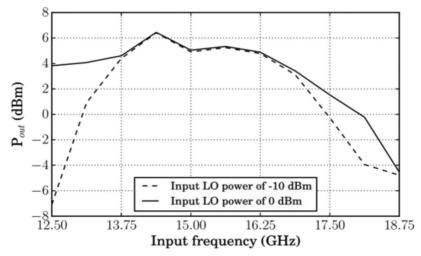

|   |             |          | 6.1.2.1       | W-band low-noise amplifier (LNA)      |     |

|   |             |          |               | with 0.5 V supply voltage             | 247 |

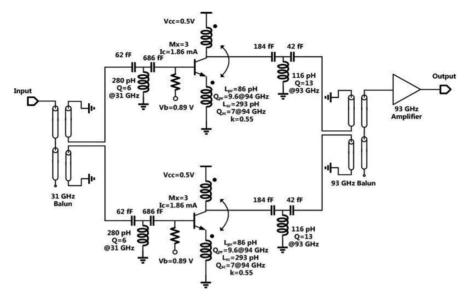

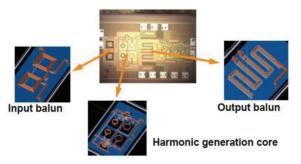

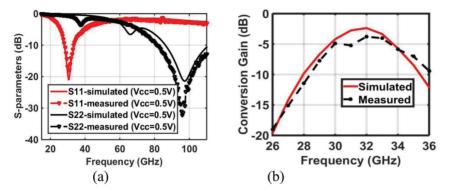

|   |             |          | 6.1.2.2       | W-band low-power frequency tripler    | 251 |

|   | 6.2         | Millim   | neter-wave    | and Terahertz Systems                 | 254 |

|   |             | U. Pfei  | iffer, R. Jai | n, J. Grzyb and P. Hillger            |     |

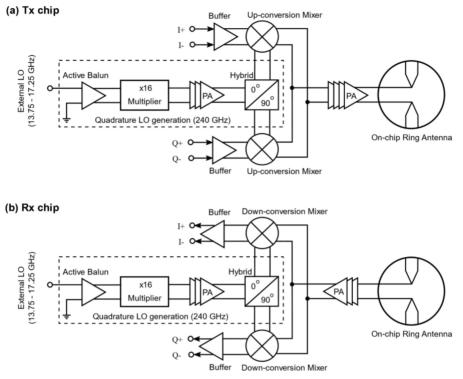

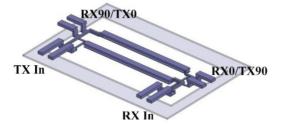

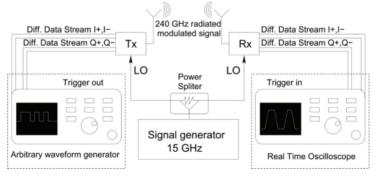

|   |             | 6.2.1    | 240 GHz       | SiGe Chipset                          | 255 |

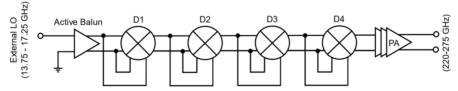

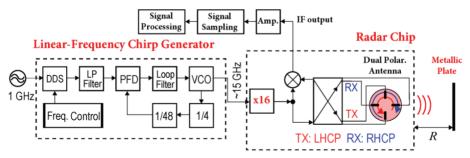

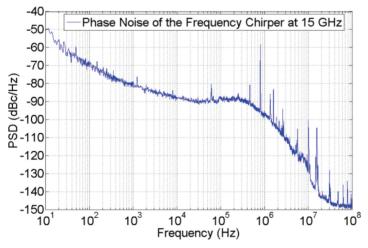

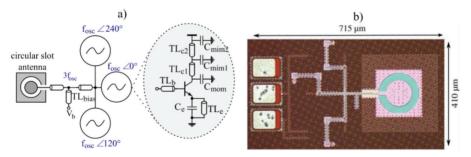

|   |             |          | 6.2.1.1       | Wideband LO signal generation         | 256 |

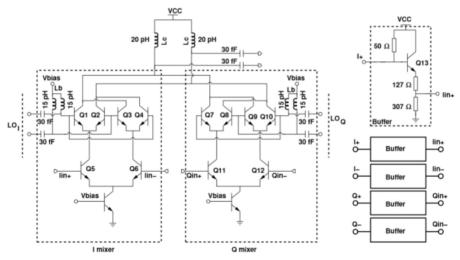

|   |             |          | 6.2.1.2       | Transmitter building blocks           | 266 |

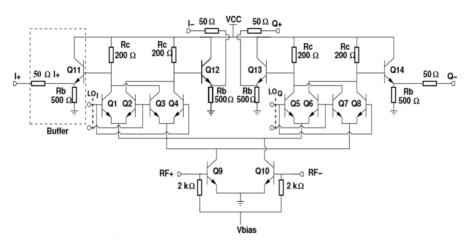

|   |             |          | 6.2.1.3       | Receiver building blocks              | 267 |

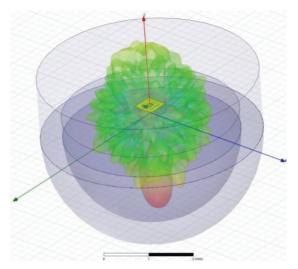

|   |             |          | 6.2.1.4       | Antenna design                        | 268 |

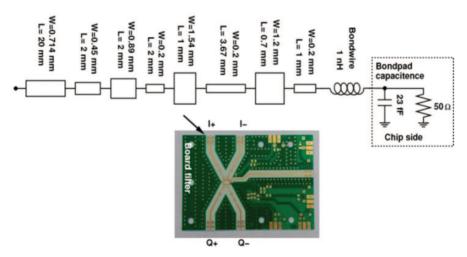

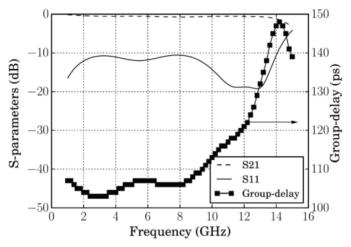

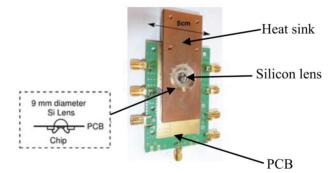

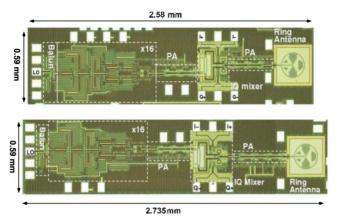

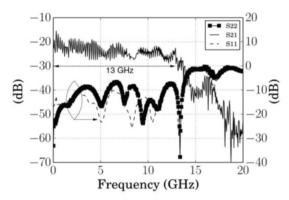

|   |             |          | 6.2.1.5       | Packaging and high-speed PCB design   | 269 |

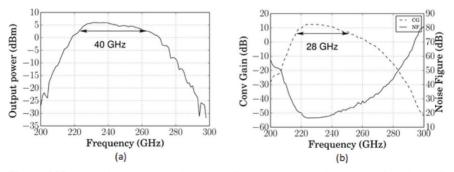

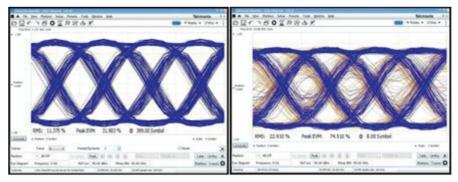

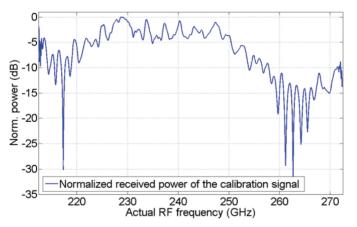

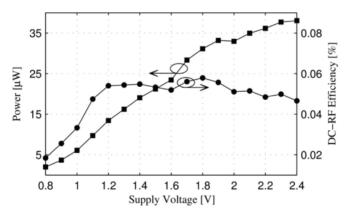

|   |             |          | 6.2.1.6       | Tx and Rx characterization            | 270 |

|   |             |          | 6.2.1.7       | Ultra-high data rate wireless         |     |

|   |             |          |               | communication                         | 273 |

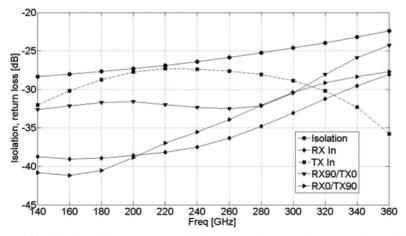

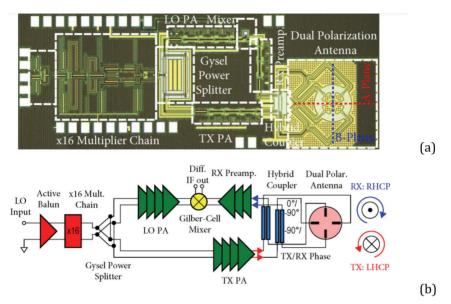

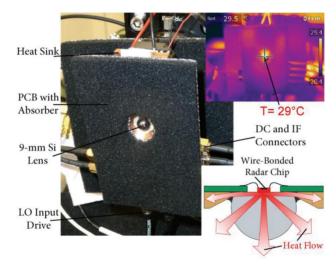

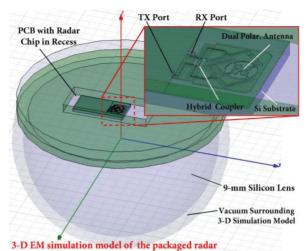

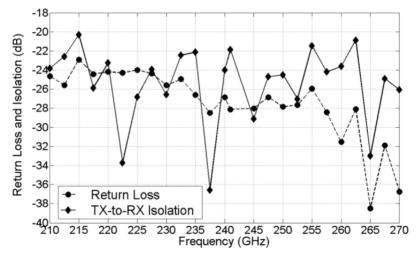

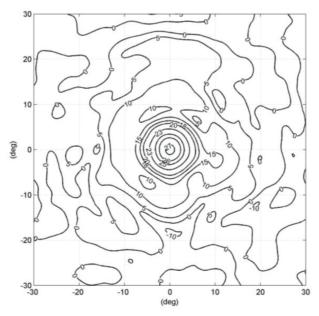

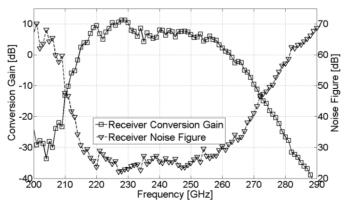

|   |             | 6.2.2    | 210-270       | GHz Circularly Polarized Radar        | 274 |

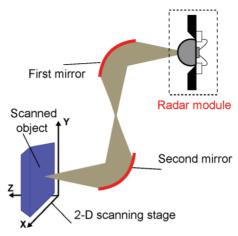

|   |             | 6.2.3    | 0.5 THz       | Computed Tomography                   | 289 |

|   |             |          | 6.2.3.1       | Components                            | 292 |

|   |             |          |               |                                       |     |

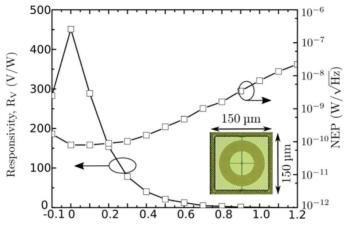

|    |                     | 6.2.3.2 Detector design                        | 294 |  |

|----|---------------------|------------------------------------------------|-----|--|

|    |                     | 6.2.3.3 THz-CT results                         | 296 |  |

|    |                     | References                                     | 298 |  |

| 7  | Futu                | re of SiGe HBT Technology and Its Applications | 309 |  |

|    | <i>M</i> . <i>S</i> | chröter, U. Pfeiffer and R. Jain               |     |  |

|    | 7.1                 | Introduction                                   | 309 |  |

|    | 7.2                 | Technology Comparison                          | 309 |  |

|    | 7.3                 | Future Millimeter-wave and THz Applications    | 315 |  |

|    |                     | 7.3.1 Communication                            | 316 |  |

|    |                     | 7.3.2 Radar                                    | 319 |  |

|    |                     | 7.3.3 Imaging and Sensing                      | 320 |  |

|    |                     | References                                     | 321 |  |

| In | Index               |                                                |     |  |

| Al | About the Editors   |                                                |     |  |

## Preface

The demand for high-speed circuits and systems has steadily increased over time. Led initially by automotive safety (radar), silicon-germanium (SiGe) heterojunction bipolar transistors (HBTs) and their combination with complementary metal-oxide-semiconductor (CMOS) transistors into highly integrated BiCMOS process technologies have become a very attractive solution for a plethora of present and prospective applications operating at frequencies from 30 GHz up to several 100 GHz (so-called mm-waves). Such applications range from communications (presently driven by 5G) to imaging in public transportation (security), medicine and biology, just to name a few. Requiring device performance beyond CMOS, above applications were traditionally placed into the realm of III-V technologies. With the goal of providing highly integrated and cost effective mm-wave electronic systems employing high-speed SiGe HBT front-end circuitry integrated with high density CMOS digital processing capability, the two European Commission funded joint research projects DOTFIVE (2007-2010) and DOTSEVEN (2013-2016) were instrumental in making SiGe HBTs and BiCMOS technology competitive and attractive for the above mentioned applications.

DOTSEVEN was a highly successful project, which not only lifted SiGe HBT performance to an unprecedented level but also provided the theoretical understanding of this new HBT technology as well as the demonstration of its capabilities. Key to the project's success was the excellent cooperation within the consortium consisting of partners from the different and complementary areas of process engineering, device modeling and circuit design. This book summarizes the important results of DOTSEVEN in more detail than the many associated publications and thus addresses not only expert readers familiar with the technology but also students and others who like to learn more about SiGe HBT technology or need a concise overview in one of the associated research areas. In each chapter, the research described is motivated and put in perspective by an introduction that provides sufficient background and additional literature for supporting the understanding. Not covered though are fundamentals of device physics, process technology and circuit design. Here, the reader is referred to the standard text books in each area.

This book is organized as follows. The Introduction provides the motivation for pursuing HBTs, in particular those based on SiGe, and for setting-up the DOTSEVEN project. Its organization and a brief description of the various work packages are presented, which mirror the relevance of the respective topics for the project. Here, also the most important results are briefly summarized in a single place.

Chapter 1 "SiGe HBT Technology" first introduces the relevant metrics used to evaluate transistor performance. Then, those HBT device and process architectures are explored that have been pursued within DOTSEVEN. It is shown why the conventional double-polysilicon self-aligned selective epitaxial growth approach limits the simultaneous increase of transit and power gain cut-off frequency. The solutions overcoming these issues and leading to the new vertical and lateral architecture developed within DOTSEVEN is described and documented by experimental results.

Chapter 2 "Device Simulation" addresses different types of numerical simulation and visualizes the results through many examples. First, the simulation of isothermal (in terms of the device temperature) carrier transport is discussed. In particular, deterministic solutions for the Boltzmann transport equation and the trade-offs necessary for applying computationally more efficient simulation approaches for device optimization are described as they were pursued within the project. The second part covers electro-thermal simulation based on coupling the impact of phonon scattering and corresponding self-heating with carrier transport simulation. The resulting simulated temperature increase is used to develop methods for accurately determining the thermal resistance from the simulated DC characteristics. Third, hot-carrier effects in advanced SiGe HBTs are investigated employing microscopic simulation.

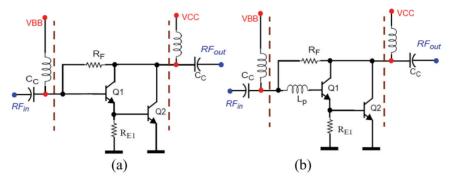

Chapter 3 "SiGe HBT Compact Modeling" starts with an overview on the standard HBT compact model HICUM Level 2. Afterwards, the most recent extensions related to DOTSEVEN, which were mostly targeted towards the intrinsic device operation are described. This is followed by a detailed discussion of the corresponding parameter extraction methods, including bias, geometry and temperature dependence. Geometry scaling and modeling of the intra-device substrate coupling concludes this chapter.

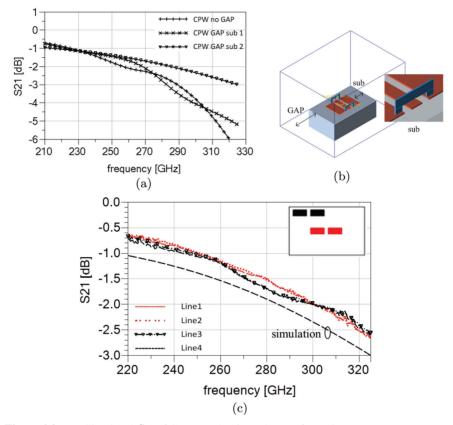

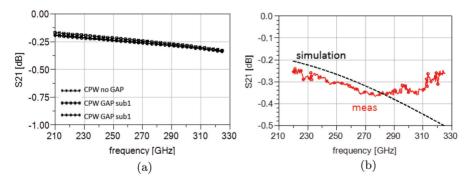

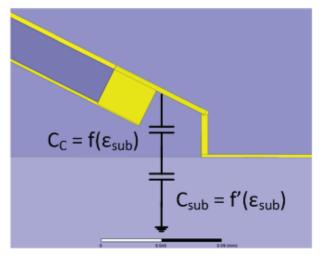

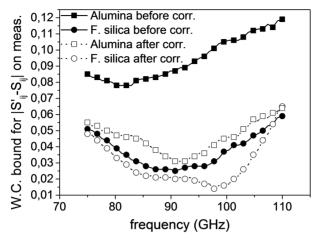

Chapter 4 "(Sub)mm-wave Calibration" addresses the electrical high-frequency on-wafer characterization of the fabricated HBTs, which

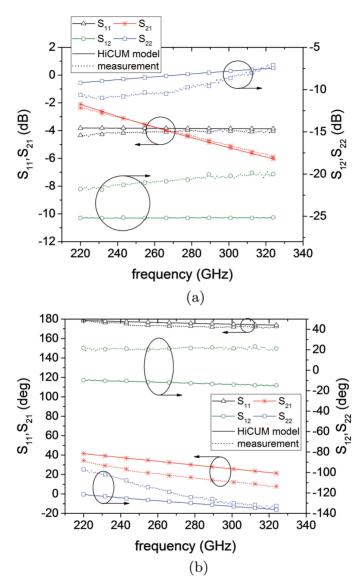

becomes inaccurate beyond 220 GHz when using traditional methods. The conventional calibration and deembedding techniques are reviewed, followed by a discussion of the signal propagation modes in transmission lines on lossy substrates as they are encountered on a silicon wafer. Direct on-wafer calibration up to the device-under-test ports is then introduced, using a special transmission line configuration. As a demonstration, a comparison of measurements using this technique with HICUM is shown for frequencies up to 325 GHz.

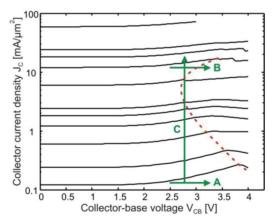

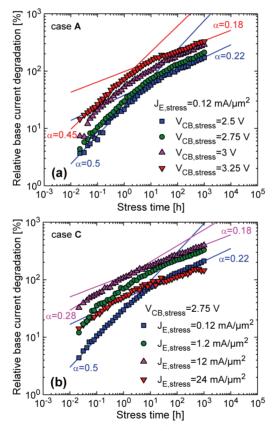

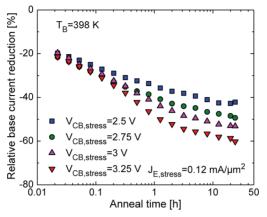

Chapter 5 "Reliability" reports on the medium- and long-term degradation of the fabricated advanced HBTs due to hot carrier stress. The measured impact of hot carriers generated during device operation on DC and low-frequency noise characteristics is shown and compared to the results of a correspondingly extended HICUM version. Furthermore, self-heating is investigated, which is becoming increasingly important in downscaled high-performance devices and plays an important role in device degradation. A method for determining the thermal resistance is described and corroborated on thermal simulation data. Finally, different analytical models for describing the thermal resistance as a function of geometry are compared.

Chapter 6 "Millimeter-wave Circuits and Applications" is divided into three parts. First, simple basic building blocks termed benchmark circuits are considered which serve mostly for verifying the compact models in a circuit environment, but can also be used for benchmarking the technology performance. For each of the selected examples a sensitivity study reveals the most important transistor parameters. The second part reports on larger circuit building blocks as they would be used in a system. Examples are given that demonstrate competitive high-frequency circuit operation down to 0.5 V supply voltage and thus very low power consumption. The third part describes the three mm-wave demonstrator systems and their building blocks that were realized with DOTSEVEN technology, namely a 240 GHz Transceiver for ultra-high data rate wireless communication, a 210–270 GHz circularly polarized radar, and a 0.5 THz computer tomography system. The latter is the first-ever purely silicon based tomography system operating at such frequency.

Chapter 7 "Future of SiGe HBT Technology and Its Applications" puts the DOTSEVEN results in perspective by comparing, based on the standard performance metrics, the different technology options for mm-wave and future sub-mm-wave applications. A more intriguing perspective is provided when looking at the transistor operation within circuits, where the load xiv Preface

comprised of parasitics from connections to other devices and the latter themselves paints a different picture of transistor speed as given by standard metrics. In view of the ITRS/IRDS roadmap for SiGe HBTs, which grew out of the modeling effort in DOTFIVE and DOTSEVEN, it is shown that HBTs in general have a bright future for realizing high-frequency systems. Their near future is discussed for different (sub-)mm-wave application areas based on DOTSEVEN results as a reference.

We hope that this book is a useful reference for a wide range of readers interested in mm- and sub-mm-wave technology, devices, and applications.

Naples and Dresden/San Diego February 2018 Niccolo Rinaldi Michael Schröter

## Acknowledgements

This work was supported by the European Commission under the contract No. 316755-DOTSEVEN. Fruitful collaboration with all partners of the DOTSEVEN consortium is gratefully acknowledged. In particular, the authors gratefully acknowledge the numerous contributions of the HBT development teams of IHP and Infineon with special thanks to: R. Barth, A. Fox, J. Korn, T. Lenke, S. Marschmeyer, A. Scheit, D. Schmidt, and D. Wolansky of IHP, and J. Böck, S. Boguth, K. Knapp, R. Lachner, W. Liebl, D. Manger, T. F. Meister, and A. Pribil of Infineon. We thank W. Skorupa and T. Schumann of Helmholtz-Zentrum Dresden-Rossendorf and S. Häberlein of FHR Anlagenbau GmbH for their support with millisecond-annealing capabilities. The authors of chapter 3 like to thank P. Sakalas for his measurement support. The authors of chapter 4 would also like to thank the European Metrology Programme for Innovation and Research (EMPIR) Project 14IND02 "Microwave measurements for planar circuits and components", for partially supporting the reported work. The EMPIR program is co-financed by the participating countries and from the European Unions Horizon 2020 research and innovation program.

We, the editors, greatly appreciate the effort of our (co-)authors to contribute the various chapters and to spend a certainly significant portion of their busy schedule to finally bring this book to completion. We would also like to thank Mark deJong for enabling the publication of this book and Junko Nagajima who tirelessly worked through several iterations of corrections for assembling the diverse contributions into a homogeneous final version.

## List of Contributors

Anindya Mukherjee, Chair for Electron Devices and Integrated Circuits, Technische Universität Dresden, Helmholtzstr, 18, Barkhausenbau, 01062 Dresden, Germany

Andreas Pawlak, Chair for Electron Devices and Integrated Circuits, Technische Universität Dresden, Helmholtzstr, 18, Barkhausenbau, 01062 Dresden, Germany

**Alessandro Magnani**, Department of Electrical Engineering and Information Technology, University Federico II, via Claudio 80125, Naples, Italy

**Bertrand Ardouin**, *XMOD Technologies*, 74 rue G. Bonnac, 3300 Bordeaux, France

**Bernd Heinemann**, *IHP*, *Im Technologiepark 25*, 15236 Frankfurt (Oder), Germany

Christoph Jungemann, RWTH Aachen University, 52056 Aachen, Germany

**Cristell Maneux**, *Laboratory of Integration of Material to System (IMS), University of Bordeaux, Bordeaux, France*

**Gerald Wedel**, Chair for Electron Devices and Integrated Circuits, Technische Universität Dresden, Helmholtzstr, 18, Barkhausenbau, 01062 Dresden, Germany

Gerhard G. Fischer, IHP, Frankfurt (Oder), Germany

Holger Rücker, IHP, Im Technologiepark 25, 15236 Frankfurt (Oder), Germany

xviii List of Contributors

**Janusz Grzyb**, Institute for High-Frequency and Communication Technology, University of Wuppertal, Wuppertal, Germany

Klaus Aufinger, Infineon Technologies AG, Neubiberg, Germany

Luca Galatro, 1. Electronic Research Laboratory, Delft University of Technology, Mekelweg 4, 2628CD, Delft, The Netherlands 2. Vertigo Technologies B.V., Mekelweg 4, 2628CD, Delft, The Netherlands

**Michael Schröter**, 1. Chair for Electron Devices and Integrated Circuits, Technische Universität Dresden, Helmholtzstr, 18, Barkhausenbau, 01062 Dresden, Germany

2. Department of Electrical and Computer Engineering, University of California at San Diego, 9500 Gilman Drive, La Jolla, CA 92093-0407, USA

**Marco Spirito**, *Electronic Research Laboratory*, *Delft University of Technology*, *Mekelweg 4*, 2628CD, *Delft*, *The Netherlands*

**Niccolò Rinaldi**, Department of Electrical Engineering and Information Technology, University Federico II, via Claudio 80125, Naples, Italy

**Philipp Hillger**, *Institute for High-Frequency and Communication Technology, University of Wuppertal, Wuppertal, Germany*

**Ritesh Jain**, Institute for High-Frequency and Communication Technology, University of Wuppertal, Wuppertal, Germany

**Salvatore Russo**, Department of Electrical Engineering and Information Technology, University Federico II, via Claudio 80125, Naples, Italy

**Ullrich Pfeiffer**, Chair for the Institute for High-Frequency and Communication Technology (IHCT), University of Wuppertal, Wuppertal, Germany

**Vincenzo d'Alessandro**, Department of Electrical Engineering and Information Technology, University Federico II, via Claudio 80125, Naples, Italy

**Wenfeng Liang**, Chair for Electron Devices and Integrated Circuits, Technische Universität Dresden, Helmholtzstr, 18, Barkhausenbau, 01062 Dresden, Germany

# **List of Figures**

| Figure 1   | List of DOTSEVEN project partners and their                      |    |

|------------|------------------------------------------------------------------|----|

|            | home countries.                                                  | 2  |

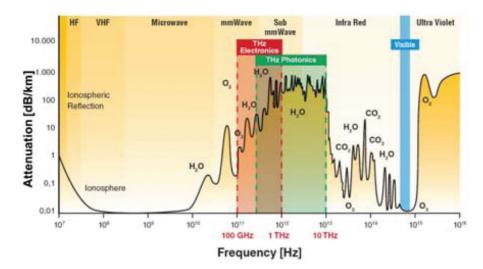

| Figure 2   | Location of the THz frequency range within                       |    |

|            | the electromagnetic spectrum. The overlap region                 |    |

|            | (THz-gap) between electronic and photonic                        |    |

|            | approaches around 1 THz is indicated                             | 4  |

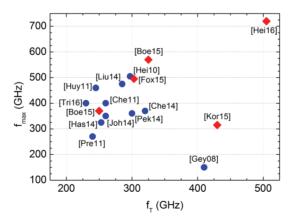

| Figure 1.1 | Peak $f_{\rm T}$ and $f_{\rm MAX}$ values of high-speed SiGe HBT |    |

|            | technologies. Red diamonds indicate results                      |    |

|            | of the DOTSEVEN project.                                         | 12 |

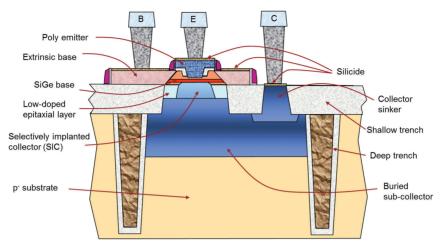

| Figure 1.2 | Schematic cross section of a high speed SiGe                     |    |

|            | HBT                                                              | 14 |

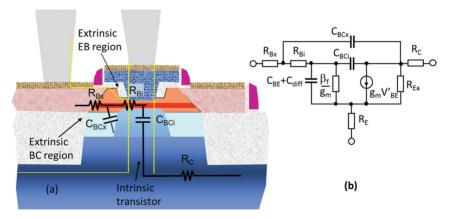

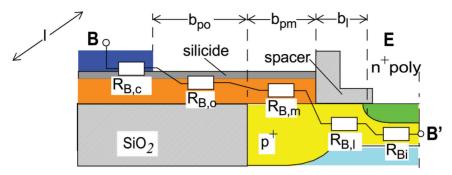

| Figure 1.3 | Device cross section with parasitic resistances                  |    |

|            | and capacitances associated with different device                |    |

|            | regions (a) and a corresponding small signal                     |    |

|            | equivalent circuit (b)                                           | 14 |

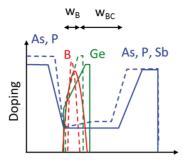

| Figure 1.4 | Schematic vertical doping profile of a SiGe HBT.                 |    |

|            | The dashed lines indicate a scaled profile                       |    |

|            | for enhanced $f_{T}$                                             | 17 |

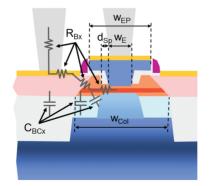

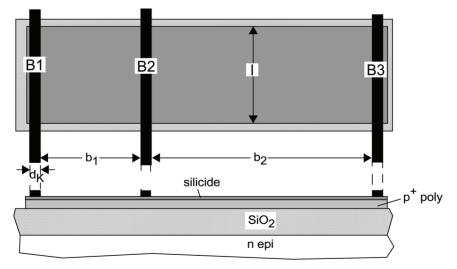

| Figure 1.5 | Device cross section with lateral device dimensions              |    |

|            | and major contributions of the base-link region                  |    |

|            | to $R_{\rm B}$ and $C_{\rm BC}$ .                                | 18 |

| Figure 1.6 | Schematic cross sections of conventional                         |    |

|            | DPSA-SEG process flow                                            | 22 |

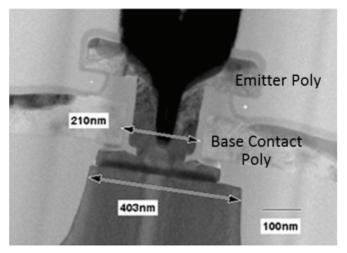

| Figure 1.7 | TEM cross section of a DPSA-SEG HBT                              |    |

|            | of Infineon's B11HFC technology.                                 | 23 |

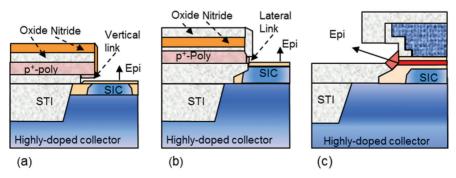

| Figure 1.8 | Different base link configurations of selective                  |    |

|            | epitaxial growth (SEG) HBTs                                      | 24 |

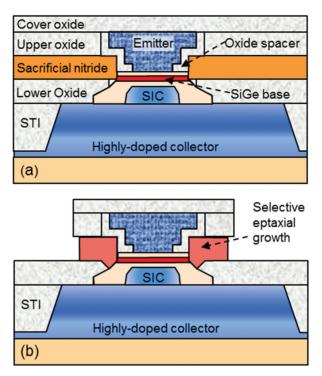

| Figure 1.9 | Schematic cross sections of the EBL process flow                 |    |

|            | after emitter structuring (a) and after selective                |    |

|            | growth of the EBL (b). $\ldots$ $\ldots$ $\ldots$ $\ldots$       | 26 |

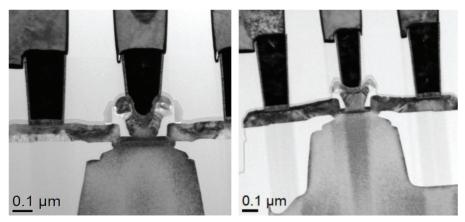

| Figure 1.10   | TEM cross section of IHP's EBL-HBT module                          |    |

|---------------|--------------------------------------------------------------------|----|

| 0             | on Infineon's 130 nm platform for the bipolar-only                 |    |

|               | run ( <i>left</i> ) and full BiCMOS flow ( <i>right</i> ).         | 29 |

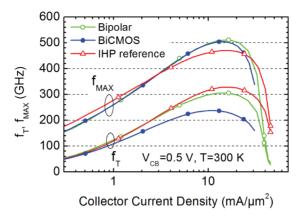

| Figure 1.11   | Transit frequency $f_{\rm T}$ and maximum oscillation              |    |

| 8             | frequency $f_{\text{MAX}}$ vs. the collector current density       |    |

|               | $j_{\rm C}$ for Infineon/IHP EBL fabrication in a bipolar-         |    |

|               | only process and in a BiCMOS run vs. the IHP                       |    |

|               | EBL reference.                                                     | 31 |

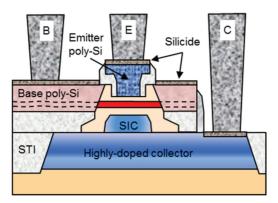

| Figure 1.12   | Schematic cross section of an NSEG HBT                             | 01 |

| I Iguite Itil | with elevated extrinsic base regions.                              | 34 |

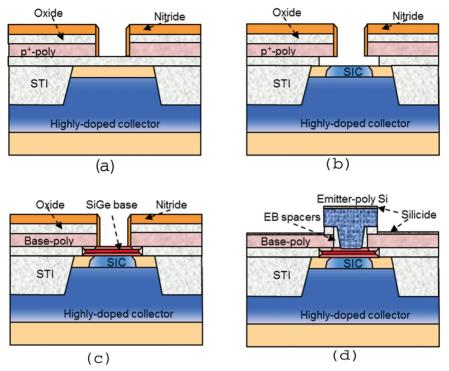

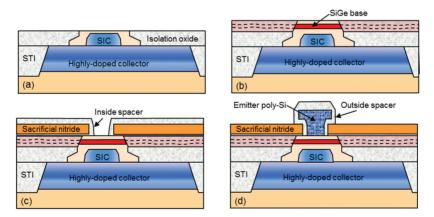

| Figure 1.13   | Process sequence for the NSEG HBT with elevated                    | 51 |

| I iguite 1.15 | base regions: (a) after SIC formation, (b) after                   |    |

|               | non-selective growth of the base, (c) before                       |    |

|               | emitter deposition, (d) after emitter structuring.                 | 34 |

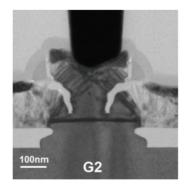

| Figure 1.14   | TEM cross section of an NSEG HBT of the                            | 54 |

| Figure 1.14   | technology SG13G2.                                                 | 35 |

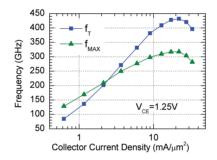

| Figure 1.15   | $f_{\rm T}$ and $f_{\rm MAX}$ vs. collector current density for an | 55 |

| Figure 1.15   | HBT with BEC layout configuration. Eight HBTs                      |    |

|               | in parallel with individual emitter areas                          |    |

|               | of $0.17 \times 1.01 \ \mu\text{m}^2$ were measured                | 37 |

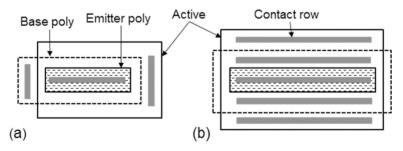

| Figure 1.16   | Layout configurations: (a) BEC configuration with                  | 57 |

| Figure 1.10   | base and collector contacts at the ends of the                     |    |

|               | emitter line, (b) CBEBC configuration with base                    |    |

|               | and collector contact rows parallel to the emitter                 |    |

|               |                                                                    | 37 |

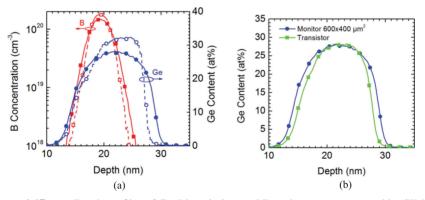

| Figure 1 17   | (a) Depth profiles of Ge (blue circles) and B (red                 | 57 |

| Figure 1.17   | squares) measured by SIMS. Open symbols                            |    |

|               | are as-grown profiles. Filled symbols are profiles                 |    |

|               | after the full fabrication process. (b) Ge depth                   |    |

|               | profiles measured by EDX in a 600 $\mu$ m $\times$ 400 $\mu$ m     |    |

|               | window (blue) and in a typical HBT structure                       |    |

|               |                                                                    | 38 |

| Figure 1 10   | (green)                                                            | 30 |

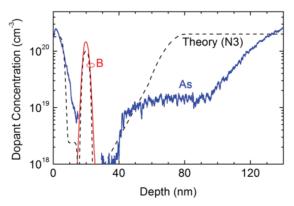

| Figure 1.18   |                                                                    |    |

|               | step. The theoretically proposed doping profile N3                 | 20 |

| Figure 1 10   | of is shown for comparison                                         | 39 |

| Figure 1.19   | Measured and simulated $f_{\rm T}$ vs. collector current           |    |

|               | density. Simulations were performed with                           |    |

|               | the hydrodynamic model in 2D and 1D. Results                       |    |

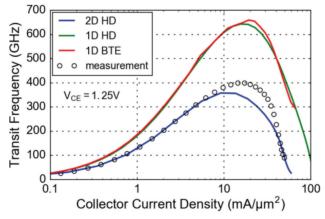

|             | obtained from the 1D Boltzmann transport equation are shown for comparison. The measured device has an emitter area of 0.28 $\mu m \times 5.0 \ \mu m$ and the CBEBC layout corresponding to Figure 1.16(b)                                                                                                                                     | 40 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

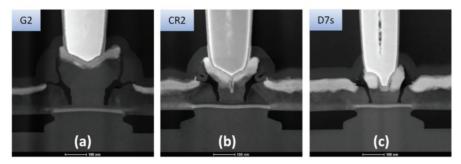

| Figure 1.20 | TEM cross sections of HBTs from the process splits G2 (a), CR2 (b), and D7s (c)                                                                                                                                                                                                                                                                 | 42 |

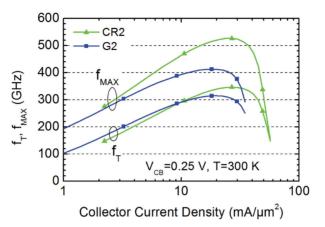

| Figure 1.21 | Transit frequency $f_{\rm T}$ and maximum oscillation<br>frequency $f_{\rm MAX}$ vs. collector current density<br>for devices of the split CR2 (second circuit<br>fabrication run in DOTSEVEN) compared<br>to the reference process G2. Device dimensions                                                                                       |    |

| Figure 1.22 | are given in Table 1.3                                                                                                                                                                                                                                                                                                                          | 43 |

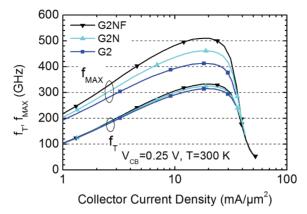

| Figure 1.23 | are given in Table 1.3                                                                                                                                                                                                                                                                                                                          | 44 |

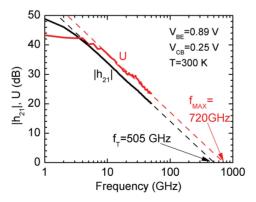

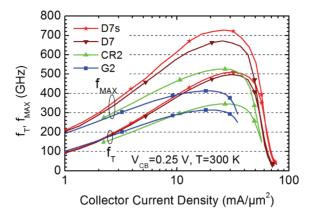

| Figure 1.24 | The emitter area is $8 \times (0.105 \times 1.0) \ \mu m^2$ Transit frequency $f_T$ and maximum oscillation frequency $f_{MAX}$ vs. collector current density for two device geometries (D7 and D7s) of the latest process status of DOTSEVEN compared to the reference process G2 and the split CR2. Device dimensions are given in Table 1.3. | 45 |

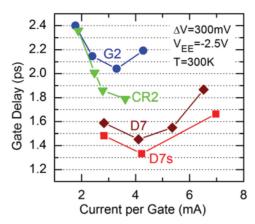

| Figure 1.25 | CML ring oscillator gate delays vs. current<br>per gate for oscillators consisting of 31 stages<br>with single-emitter HBTs for the splits G2 ( $A_{\rm E} =$<br>0.12 µm × 1.02 µm), CR2 ( $A_{\rm E} = 0.1$ µm × 1.0 µm),<br>D7, and D7s ( $A_{\rm E} = 0.105$ µm × 1.02 µm)                                                                   | 40 |

#### xxii List of Figures

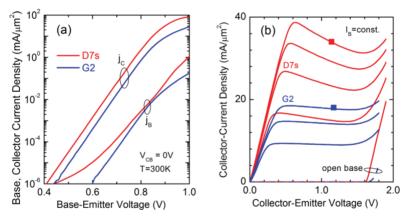

| Figure 1.26 | Gummel characteristics (a) and base-current forced                                      |    |

|-------------|-----------------------------------------------------------------------------------------|----|

| 0           | output characteristics (b) for the splits D7s and G2.                                   |    |

|             | Symbols in (b) indicate the bias points for peak $f_{\rm T}$ .                          |    |

|             | The emitter areas are $8 \times (0.12 \times 1.02) \mu\text{m}^2$ for G2                |    |

|             | and 8 × (0.105 × 1.0) $\mu$ m <sup>2</sup> for D7s                                      | 47 |

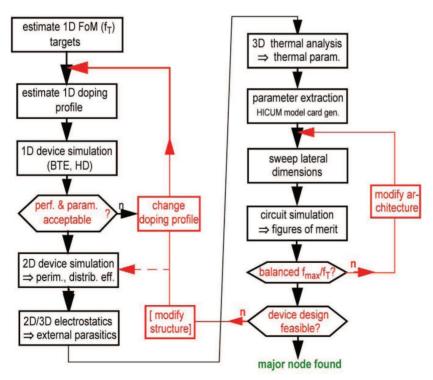

| Figure 2.1  | Flowchart for finding the vertical and lateral HBT                                      |    |

| 8           | structure of a major technology node                                                    | 56 |

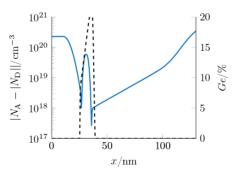

| Figure 2.2  | Net doping and Germanium profile of a SiGe HBT                                          |    |

| 8           | with $f_{\rm T} = 630$ GHz.                                                             | 66 |

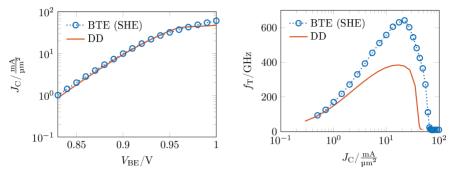

| Figure 2.3  | Transfer characteristic (left) and transit frequency                                    |    |

| 0           | (right) obtained from DD transport and BTE for the                                      |    |

|             | device of Figure 2.2. $V_{CE} = 1 V_{}$                                                 | 67 |

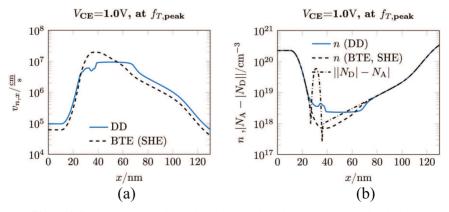

| Figure 2.4  | Electron velocity and density obtained by DD and                                        |    |

| C           | BTE simulation                                                                          | 67 |

| Figure 2.5  | Illustration of the impact of $f^{td}$ on the transfer                                  |    |

|             | characteristic, transit frequency and output                                            |    |

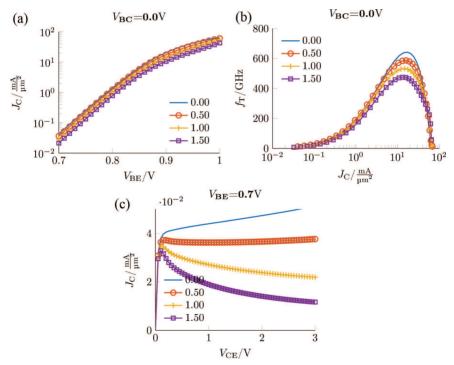

|             | characteristics for $f^{tc} = f^{ec} = 0. \dots \dots$                                  | 68 |

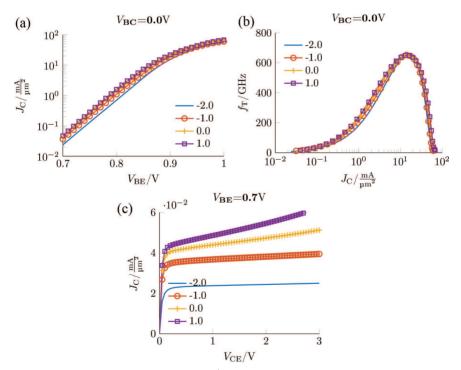

| Figure 2.6  | Illustration of the impact of $f^{tc}$ on the transfer                                  |    |

|             | characteristic, transit frequency and output                                            |    |

|             | characteristics at $f^{td} = f^{ec} = 0. \dots \dots$                                   | 69 |

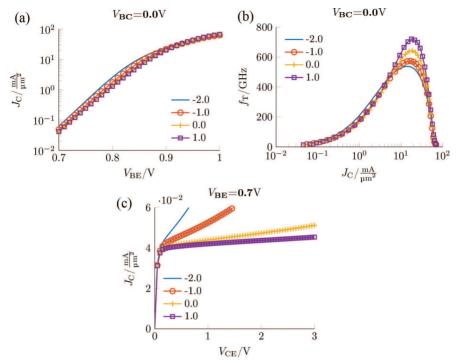

| Figure 2.7  | Exemplary illustration of the impact of                                                 |    |

|             | $f^{\text{ec}}$ ( $f^{\text{td}} = f^{\text{tc}} = 0$ ) on the transfer characteristic, |    |

|             | transit frequency and output characteristic                                             | 70 |

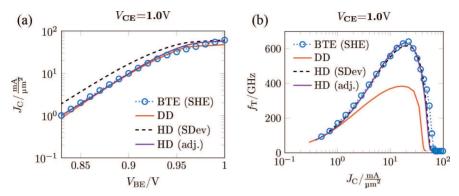

| Figure 2.8  | Transfer characteristic and transit frequency of                                        |    |

|             | the SiGe HBT in Figure 2.2 obtained from HD                                             |    |

|             | simulation with adjusted HD transport model                                             |    |

|             | parameters and SDevice defaults [Syn15], compared                                       |    |

|             | to BTE and DD simulation results                                                        | 71 |

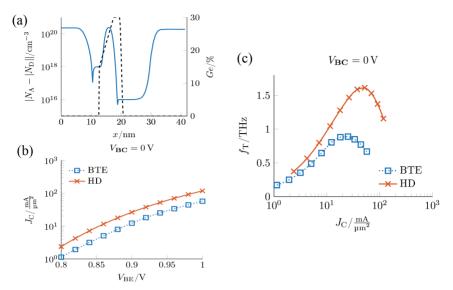

| Figure 2.9  | (a) Net doping and Ge profile of the SiGe HBT                                           |    |

|             | given in [Sch11] and the corresponding (b) transfer                                     |    |

|             | characteristic and (c) transit frequency obtained                                       |    |

|             | from BTE and HD simulation.                                                             | 72 |

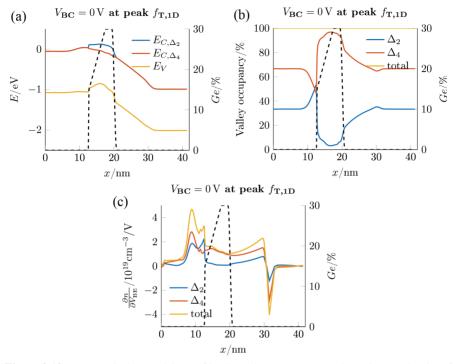

| Figure 2.10 | (a) Band edges and Ge profile, (b) valley occupancy,                                    |    |

|             | and (c) electron density of the SiGe HBT shown                                          |    |

|             | in Figure 2.9 obtained by BTE simulation at the                                         |    |

|             | operating point of peak transit frequency                                               | 73 |

| Figure 2.11 | (a) Band edges and graded Ge profile as well as the corresponding (b) valley occupancy and (c) electron |    |

|-------------|---------------------------------------------------------------------------------------------------------|----|

|             | density obtained by BTE simulation at the operating                                                     | -  |

| F' 0.10     | point of peak transit frequency.                                                                        | 74 |

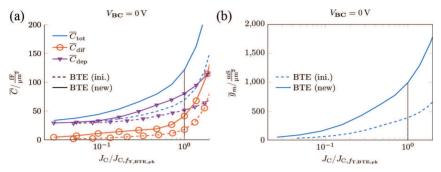

| Figure 2.12 | (a) Comparison of (a) the total 1D capacitance connected to the base node and its components and        |    |

|             | (b) the transconductance, obtained for the initial                                                      |    |

|             | (abrupt) and the new (graded) SiGe HBT                                                                  |    |

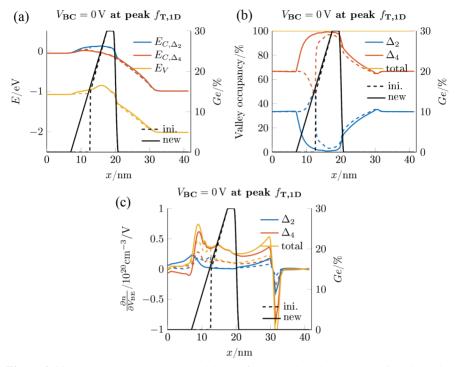

|             | profile                                                                                                 | 75 |

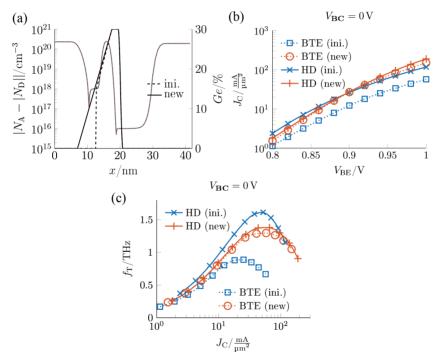

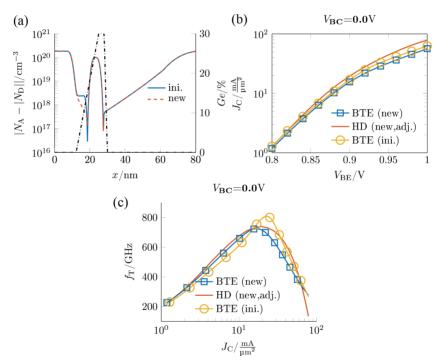

| Figure 2.13 | (a) Comparison of the initial and the new SiGe HBT                                                      |    |

| 0           | profile with corresponding (b) transfer characteristic                                                  |    |

|             | and (c) transit frequency, obtained by both BTE and                                                     |    |

|             | HD simulation.                                                                                          | 75 |

| Figure 2.14 | (a) Doping and Germanium profile of a SiGe HBT                                                          |    |

| 0           | and the corresponding (b) transfer characteristic and                                                   |    |

|             | (c) transit frequency obtained from BTE and HD                                                          |    |

|             | simulation.                                                                                             | 76 |

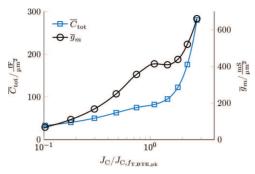

| Figure 2.15 | Transconductance and total capacitance of the N3                                                        |    |

| 0           | SiGe HBT.                                                                                               | 77 |

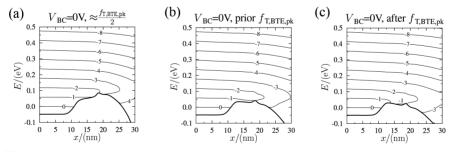

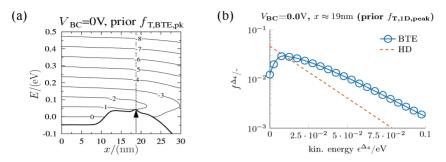

| Figure 2.16 | Conduction band edge versus location and                                                                |    |

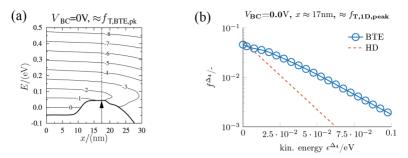

| 0           | superimposed contour lines of the (logarithm of the)                                                    |    |

|             | electron distribution function of the 4-fold $\Delta$ -valley                                           |    |

|             | over energy within the emitter-base region for three                                                    |    |

|             | operating points: (a) around $f_{T,BTE,pk}/2$ ,                                                         |    |

|             | (b) just before $f_{T,BTE,pk}$ , and (c) and just                                                       |    |

|             | after $f_{T,BTE,pk}$ .                                                                                  | 77 |

| Figure 2.17 | Electron distribution function within the                                                               |    |

|             | 4-fold $\Delta$ -valley just below $f_{T,BTE,pk}$ within the                                            |    |

|             | emitter-base region. (a) Contours with the arrow                                                        |    |

|             | marking the position of the doping induced                                                              |    |

|             | conduction band barrier. (b) Comparison of HD and                                                       |    |

|             | BTE distribution function at the barrier                                                                | 79 |

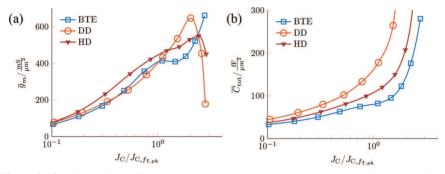

| Figure 2.18 | Comparison of (a) the transconductances and                                                             |    |

|             | (b) the total capacitance obtained by DD, HD                                                            |    |

|             | and BTE simulation results                                                                              | 79 |

### xxiv List of Figures

| Figure 2.19 | Comparison of the BTE and HD electron densities<br>obtained by (a) an DC and (b) an quasi-static<br>analysis. In (b), also the quasi-static hole densities<br>are shown. For (b), a different axis intercept is<br>used compared to (a) in order to visualize the<br>contributions to the emitter junction<br>capacitance $\overline{C}_{iEi}$ . | 80 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.20 | Comparison of $\overline{C}_{jEi}$ obtained by BTE and HD simulations.                                                                                                                                                                                                                                                                           | 81 |

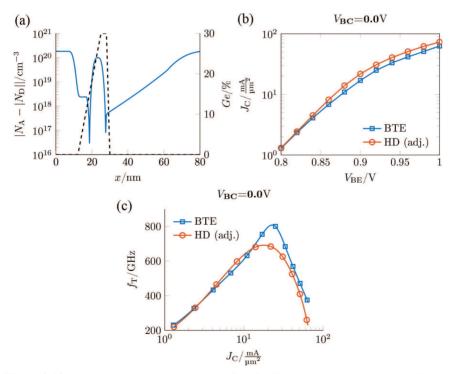

| Figure 2.21 | <ul><li>(a) Doping profile with smoothed high to low<br/>transition in the emitter (new) and previous<br/>step-like profile (ini.). Corresponding terminal<br/>characteristics: (a) transfer current and (b) transit</li></ul>                                                                                                                   | 81 |

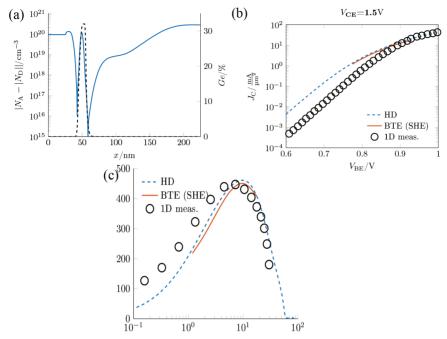

| Figure 2.22 | frequency                                                                                                                                                                                                                                                                                                                                        | _  |

| Figure 2.23 | function at the barrier peak                                                                                                                                                                                                                                                                                                                     | 82 |

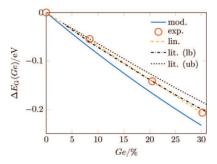

| Figure 2.24 | Comparison of the Ge concentration induced<br>bandgap narrowing from experimental data (exp.)<br>and device simulation model (mod.). In addition,<br>the lower and upper boundary (lb and ub) for<br>bandgap narrowing as function of Ge the presence                                                                                            |    |

| Figure 2.25 | of metastable strain is shown                                                                                                                                                                                                                                                                                                                    | 84 |

|             |                                                                                                                                                                                                                                                                                                                                                  |    |

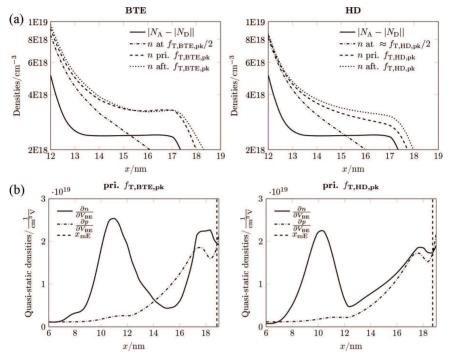

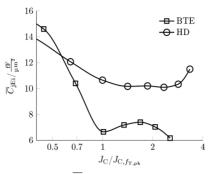

| Figure 2.26 | Comparison of the performance trends predicted                      |    |

|-------------|---------------------------------------------------------------------|----|

|             | by TCAD (HD and BTE simulation) with 1D                             |    |

|             | measurement results (three samples) for a process                   |    |

|             | split with four different SiGe HBTs (fabricated                     |    |

|             | by HP)                                                              | 85 |

| Figure 2.27 | Thermal energy transport diagram in semiconductor                   |    |

|             | devices                                                             | 86 |

| Figure 2.28 | (Top) Thermal conductivity in the 2-D SiGe HBT                      |    |

|             | structure by taking into account the effect of                      |    |

|             | Ge content, doping concentration, and boundary                      |    |

|             | scattering at 300 K. (Bottom) Self-consistent lattice               |    |

|             | temperature at $V_{\rm BE}$ = 0.9 V and $V_{\rm CE}$ = 1 V          | 90 |

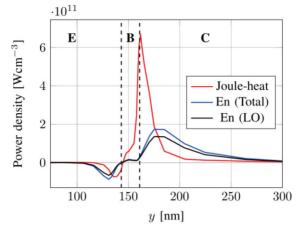

| Figure 2.29 | Profiles of the power densities received and                        |    |

|             | dissipated by carriers which are calculated from                    |    |

|             | Joule-heating and energy loss rate due to inelastic                 |    |

|             | phonon scattering, respectively, along the symmetry                 |    |

|             | axis of the HBT at $V_{\rm BE}$ = 0.9 V and $V_{\rm CE}$ = 1 V      | 91 |

| Figure 2.30 | (Top) The LO phonon distribution function (zeroth-                  |    |

|             | order harmonic), and (bottom) lattice temperature                   |    |

|             | and effective temperature for LO phonons, along the                 |    |

|             | symmetry axis of the investigated HBT at $V_{\rm BE} = 0.9$         |    |

|             | V and $V_{\rm CE}$ = 1 V                                            | 92 |

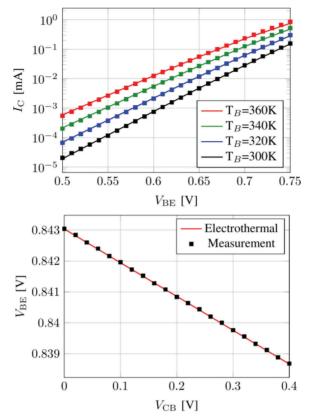

| Figure 2.31 | (Top) $I_{\rm C}$ – $V_{\rm BE}$ characteristics for different      |    |

|             | homogeneous temperatures at $V_{\rm CE}$ = 0.6 V. Solid             |    |

|             | lines show the isothermal simulation results at $T_{\rm B}$         |    |

|             | = 300, 320, 340, 360 K and symbols show the                         |    |

|             | corresponding measurement data. (Bottom) $V_{\rm BE}$ –             |    |

|             | $V_{\rm CB}$ characteristics from electrothermal simulation         |    |

|             | and measurement at $I_{\rm E}$ = 2 mA                               | 93 |

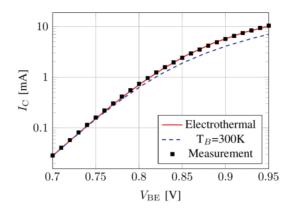

| Figure 2.32 | $I_{\rm C} - V_{\rm BE}$ characteristics with and without including |    |

|             | self-heating compared to measurement data at                        |    |

|             | $V_{\rm CE}$ = 1 V                                                  | 94 |

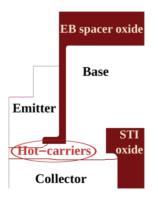

| Figure 2.33 | (Left) Creation of Si dangling bonds at the Si/SiO <sub>2</sub>     |    |

|             | interface. (Right) Passivation of the dangling bonds                |    |

|             | by incorporating hydrogen atoms.                                    | 95 |

| Figure 2.34 | Schematic of a state-of-the-art SiGe HBT with the                   |    |

|             | corresponding EB spacer and STI oxides                              | 95 |

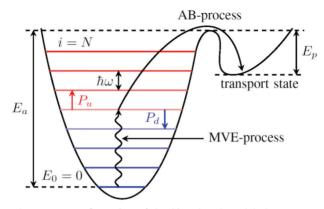

| Figure 2.35 | The energy configuration of the Si–H bond modeled                   |    |

|             | as a truncated harmonic oscillator.                                 | 97 |

### xxvi List of Figures

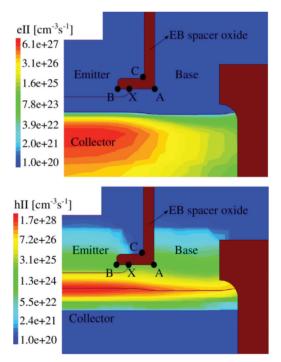

| Figure 2.36 | II generation rates in the SiGe HBT induced by                                               |     |

|-------------|----------------------------------------------------------------------------------------------|-----|

| -           | electrons (top) and holes (bottom) at P3                                                     | 100 |

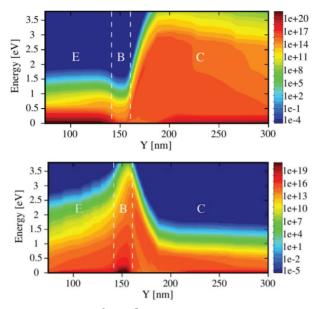

| Figure 2.37 | Cut of EDFs $[eV^{-1} cm^{-3}]$ for electrons (top) and                                      |     |

|             | holes (bottom) along the symmetry axis of the HBT                                            |     |

|             | at P3.                                                                                       | 101 |

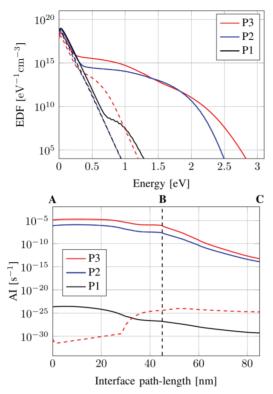

| Figure 2.38 | (Top) EDFs of electrons (dashed lines) and holes                                             |     |

| 0           | (solid lines) at the intersection of the EB spacer                                           |     |

|             | oxide interface and the EB junction [denoted by                                              |     |

|             | node X in Figure 2.36 (Bottom)]. Profiles of the                                             |     |

|             | AB AIs for electrons (dashed lines) and holes (solid                                         |     |

|             | lines) along the EB spacer oxide interface from node                                         |     |

|             | A to C denoted in Figure 2.36.                                                               | 102 |

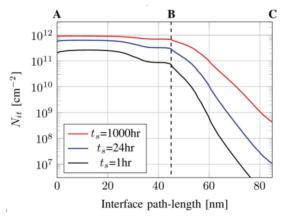

| Figure 2.39 | Interface trap densities generated at different stress                                       |     |

| 8           | time steps from node A to C denoted in Figure 2.36                                           |     |

|             | at P3                                                                                        | 103 |

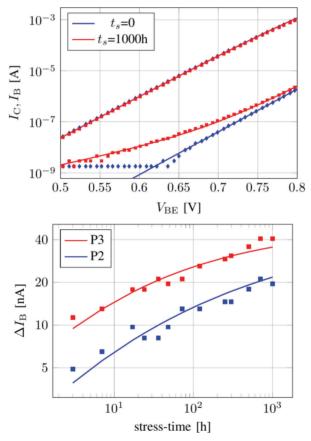

| Figure 2.40 | (Top) Gummel characteristics ( $V_{CB} = 0$ V) of the                                        |     |

| 8           | fresh and degraded SiGe HBT after 1,000 h at P3                                              |     |

|             | obtained from simulation (lines) and measurement                                             |     |

|             | (symbols). (Bottom) Excess base currents over the                                            |     |

|             | stress time obtained from simulation (lines) and                                             |     |

|             | measurement (symbols) at $V_{\rm BE}$ = 0.67 V and                                           |     |

|             | $V_{\rm CB} = 0$ V                                                                           | 104 |

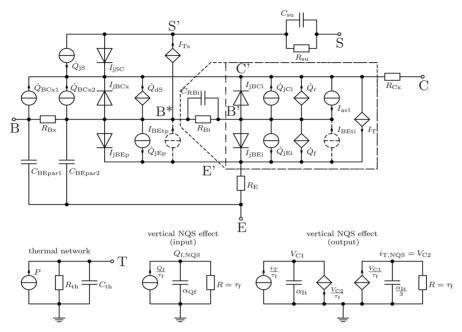

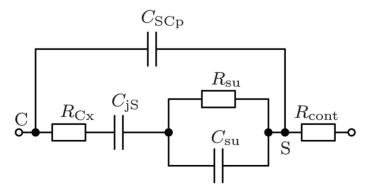

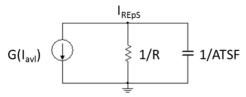

| Figure 3.1  | Equivalent circuit of HICUM/L2 including the                                                 |     |

| 0           | adjunct networks for modeling electro-thermal                                                |     |

|             | effects and NQS effects. Not shown are the                                                   |     |

|             | networks for modeling correlated noise. The                                                  |     |

|             | dash-dotted line defines the intrinsic (1D) transistor                                       |     |

|             | representation and the dashed line defines the                                               |     |

|             | internal transistor.                                                                         | 117 |

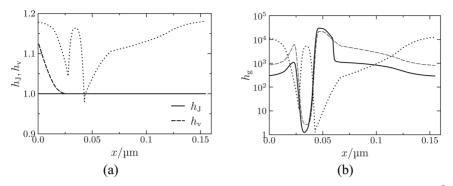

| Figure 3.2  | Spatial dependence of the weight functions (a) $h_{\rm J}$                                   |     |

|             | and $h_{\rm v}$ for $J_{\rm C} = 5 {\rm mA}/\mu{\rm m}^2$ , and (b) $h_{\rm g}$ (solid line) |     |

|             | for low injection. In both pictures the dotted line                                          |     |

|             | shows the 1D doping profile in log-scale. In (b), the                                        |     |

|             | dashed line shows the bandgap in linear scale                                                | 120 |

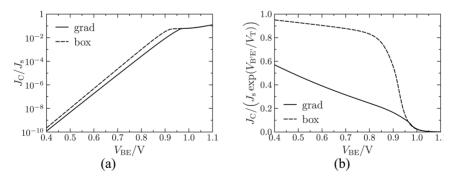

| Figure 3.3  | (a) Transfer current for transistors with different Ge                                       |     |

|             | profiles in the base. (b) Transfer current normalized                                        |     |

|             | to their ideal formulation for the same transistors as                                       |     |

|             | in (a) at room temperature and $V_{B'C'} = 0 \text{ V.} \dots$                               | 121 |

|             |                                                                                              |     |

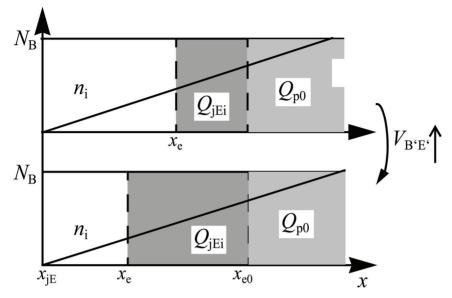

| Figure 3.4  | Visualization of the depletion charge in the                                      |     |

|-------------|-----------------------------------------------------------------------------------|-----|

| 0           | base–emitter space charge region for two bias points                              |     |

|             | with increasing voltage from the top picture to                                   |     |

|             | the bottom. The intrinsic carrier density is given                                |     |

|             | in log-scale. $x_{iE}$ relates to the metallurgic BE                              |     |

|             | junction, while $x_e$ and $x_{e0}$ , respectively, are the                        |     |

|             | boundaries of the space charge region for                                         |     |

|             | $V_{B'E'} > 0V$ and $V_{B'E'} = 0V$ , respectively                                | 123 |

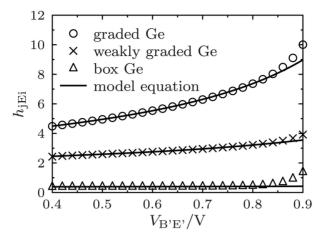

| Figure 3.5  | Application of the model Equation (3.19) for the                                  | _   |

| 8           | weight factor obtained to transistors with different                              |     |

|             | shapes of the Ge profile                                                          | 125 |

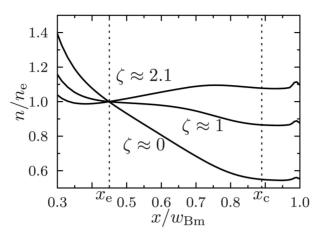

| Figure 3.6  | Spatial dependence of the electron density                                        | -   |

| 8           | normalized to $n_{\rm e}$ from (3.11) in the neutral base,                        |     |

|             | marked by the vertical dashed lines, for different                                |     |

|             | values of the field factor $\zeta$ . The <i>x</i> -axis is normalized             |     |

|             | to the metallurgical base width $w_{\rm Bm}$ with the BE                          |     |

|             | junction located at $x = 0. \ldots \ldots \ldots$                                 | 126 |

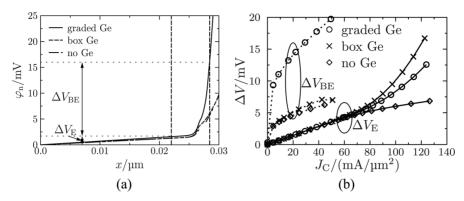

| Figure 3.7  | (a) Determination of the voltage drop in the neutral                              |     |

| 8           | emitter ( $\Delta V_{\rm e}$ ) and in the BE SCR ( $\Delta V_{\rm BE}$ ) from the |     |

|             | quasi-fermi potential of the electrons for transistors                            |     |

|             | with different Ge profiles in the base. The dashed                                |     |

|             | lines show the begin and end of the BE SCR. (b)                                   |     |

|             | Current dependence of the voltage drops; $\Delta V_{\rm BE}$ is                   |     |

|             | shown for bias points only up to the beginning of                                 |     |

|             | high current effects.                                                             | 127 |

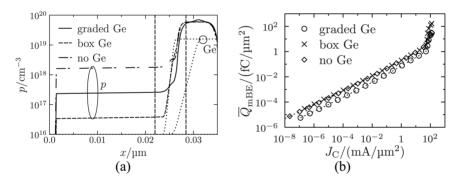

| Figure 3.8  | (a) Spatial dependence of the hole density for                                    |     |

| 8           | transistors with different Ge profiles. The Ge                                    |     |

|             | content is given by the dotted lines for the box (left)                           |     |

|             | and the graded (right) profile. The vertical dashed                               |     |

|             | lines are the same as in Figure 3.7(b) Minority                                   |     |

|             | charge as a function of collector current density in                              |     |

|             | the BE SCR for transistors with different Ge profile.                             | 127 |

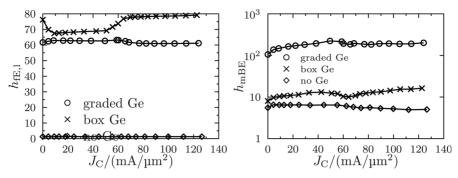

| Figure 3.9  | Current dependence of the weight factors for the                                  |     |

| 8           | charge stored in the neutral emitter and BE SCR for                               |     |

|             | the transistors with different Ge profiles                                        | 128 |

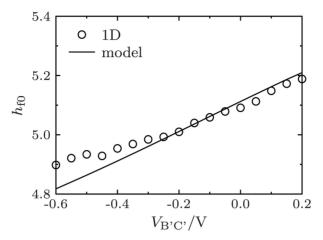

| Figure 3.10 | Bias dependence of $h_{\rm f0}$ extracted from 1D                                 | -   |

| 5           | device simulations and application of the model                                   |     |

|             | equation (3.23)                                                                   | 129 |

|             |                                                                                   | -   |

### xxviii List of Figures

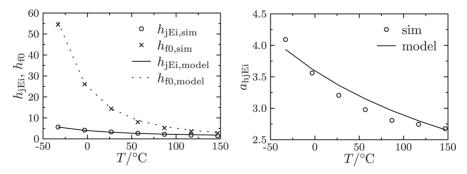

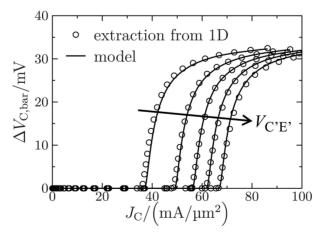

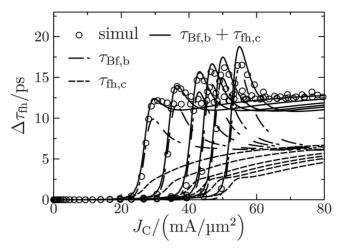

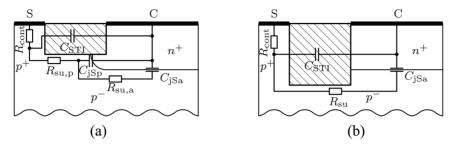

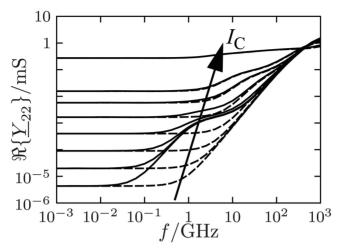

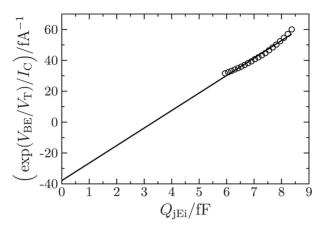

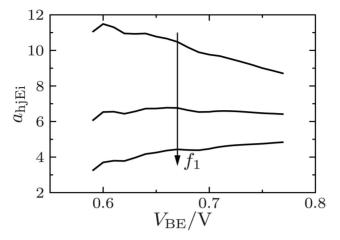

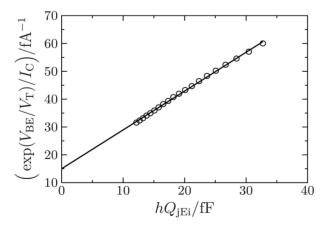

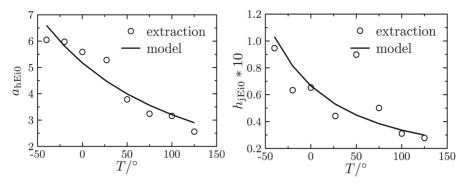

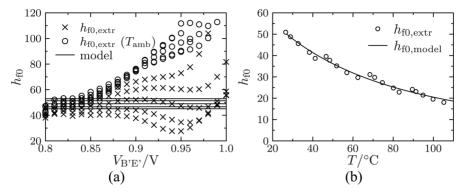

| Figure 3.11   | Application of the model equations (3.29) and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|               | (3.32) to $h_{jEi0}(T)$ and $h_{f0}(T)$ as well as Equation (3.31)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

|               | to $a_{hjEi}$ obtained from 1D device simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 131  |

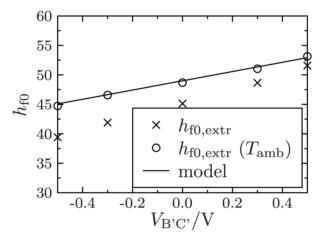

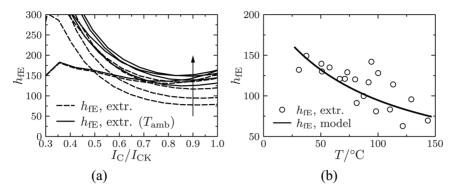

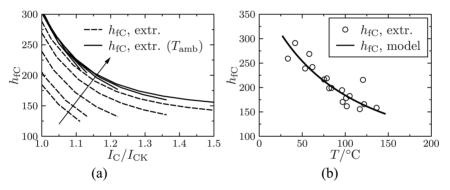

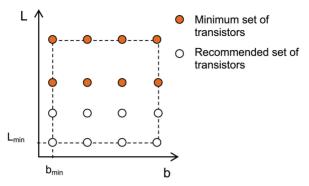

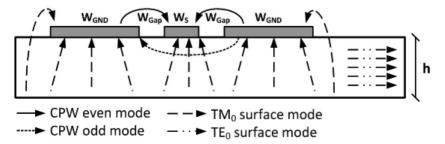

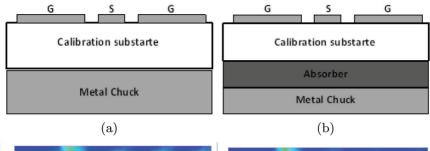

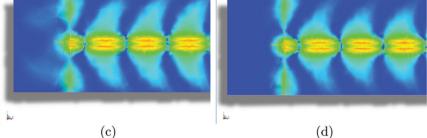

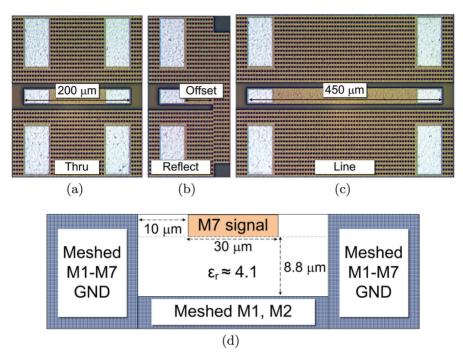

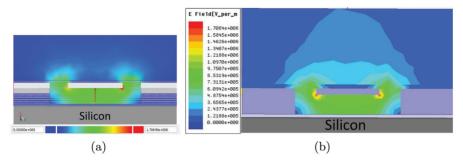

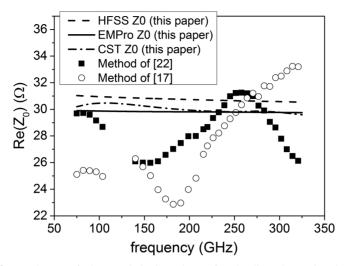

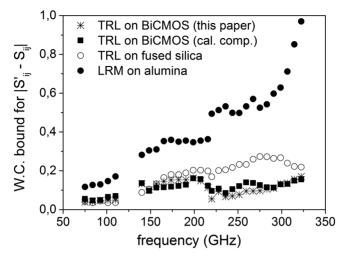

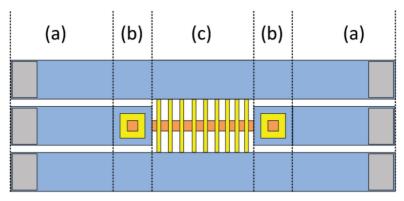

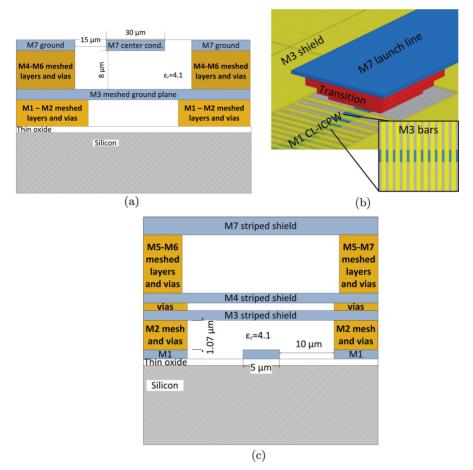

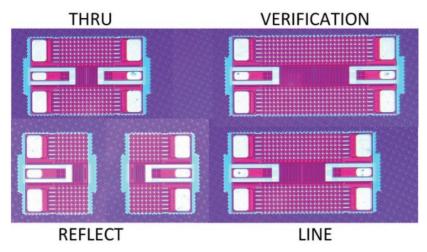

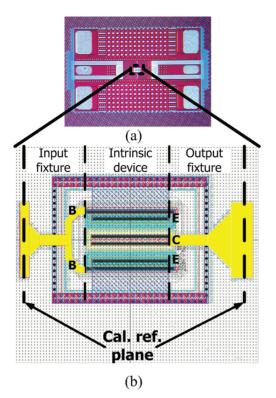

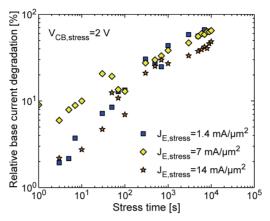

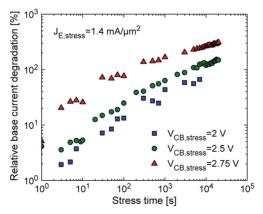

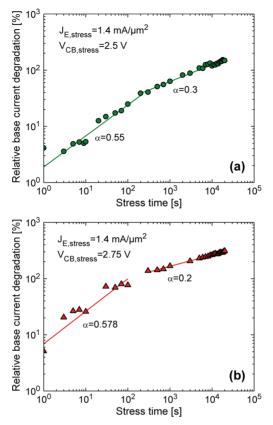

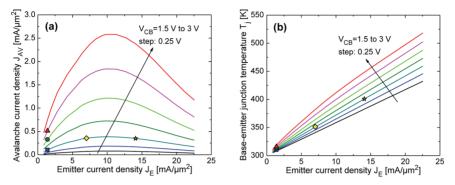

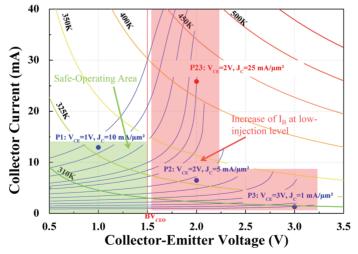

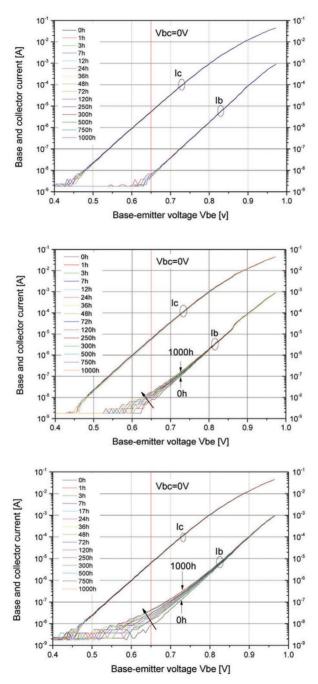

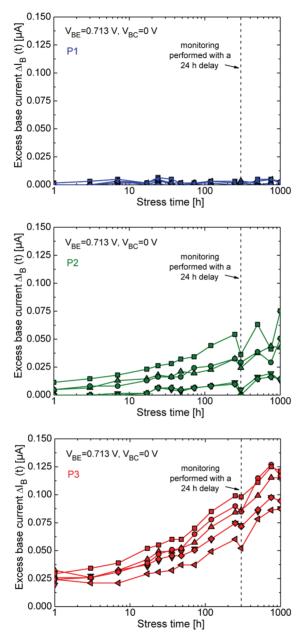

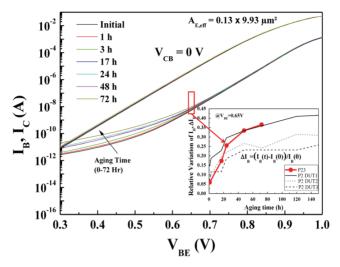

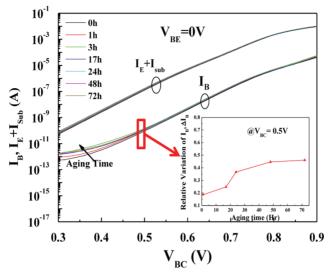

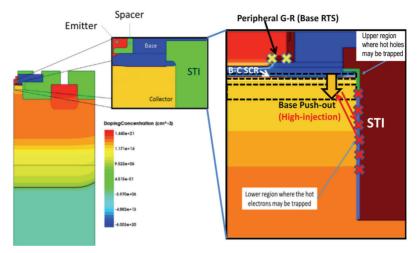

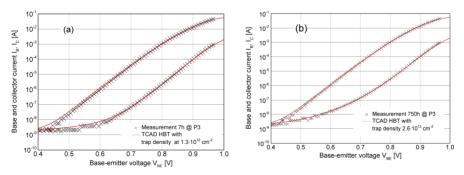

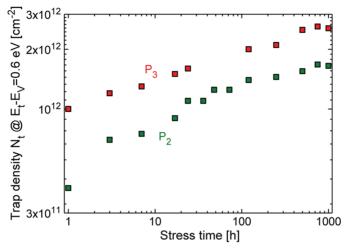

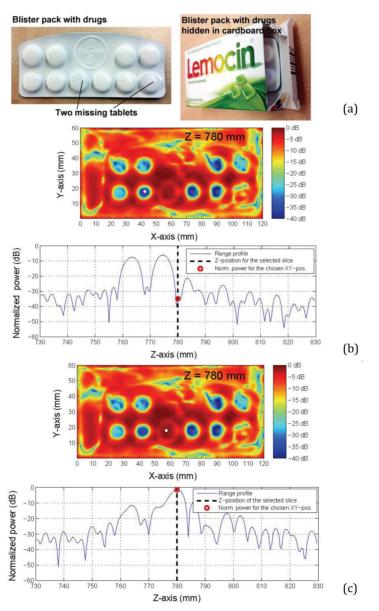

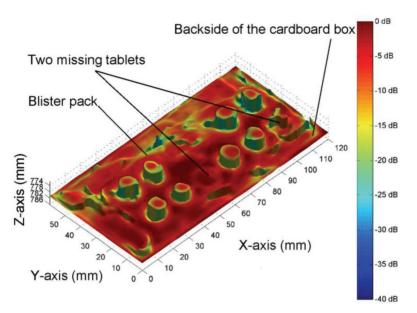

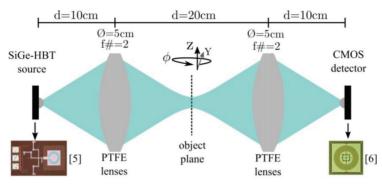

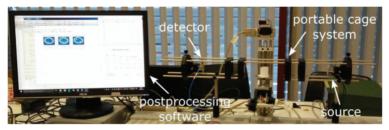

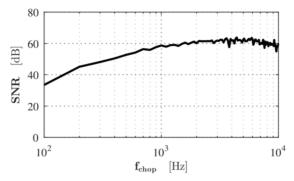

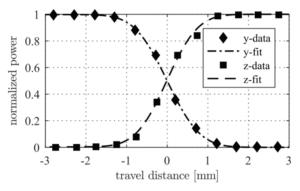

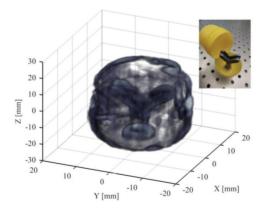

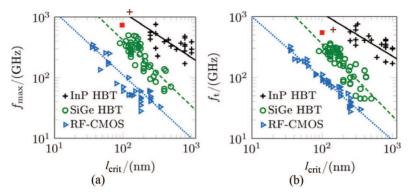

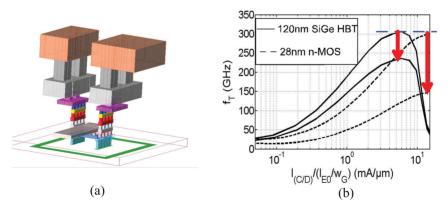

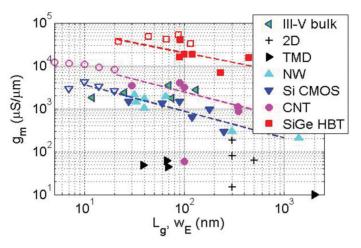

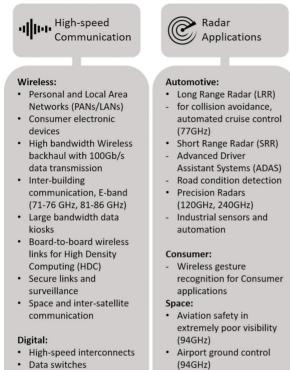

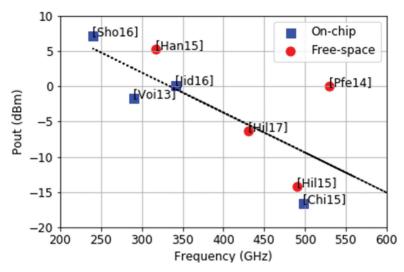

| Figure 3.12   | Application of (3.33) to the high current weight                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |