# FIR FILTER DESIGN BASED ON MCMA MODULE

Meenaakshi Sundhari R.P<sup>1</sup>.,Fathimasaffana A<sup>2</sup>., Dharanya D<sup>3</sup>.,Bridget Maria Helen E<sup>4</sup>

<sup>1</sup>Professor, Department of ECE,

*E-Mail:* rpmeenaakshi@gmail.com

<sup>2,3,4</sup>UG Scholar, Department of ECE,

*E-Mail:* afathimasaffana@gmail.com , dharanya20042001@gmail.com, bridgetmariahelen2001@gmail.com *P.A College of Engineering and Technology, Pollachi, Coimbatore, India.*

# Abstract

In many digital signal processing and communication systems, the FIR filter is a critical component. This paper depicts the construction of digital FIR filters utilizes better version of truncated multiplier which needs lower number of multipliers and adders. Here the improvement of bit width is attained without losing frequency response and last signal accuracy. To decrease the overall space the non uniform quantization with an appropriate filter is recommended. Furthermore, the recommended digital filter is efficient with respect to space and capacity when related with present FIR filter structure

Keywords:DSP, FIR Filters, Truncated multipliers, Very Large Scale Integrated structure

# 1. INTRODUCTION

For screening a binary signal FIR filter circuit is used and gives an result that is one more digital signal with properties that are decided by the output of the filter. It's also used in wide range of compact applications that demand little area and energy. The following is a representation of a basic Finite Impulse Response filter of order M,

$\mathbf{Y}(\mathbf{n}) = \sum_{i=0}^{M-1} a_i x(n-i).$

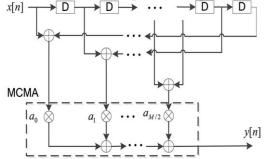

With this equation ai = aM-i or ai = -aM-I the factors symmetric nature is determined which is in linear phase. The 2 standard Finite Impulse Response direct method and transposed method structures depicts Finite Impulse Response filter having a phase which is linear and uniform arrangement. The direct structure depicts simultaneous product of all postponed signals, related filter factors are executed with MCMA module.

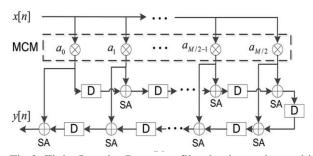

So,values of the multiplier in Multiple Constant Multipliers/Accumulators gets postponed incoming signals x(n-i) and factors. The transposed structure depicts present input signal x(n) and factors are the values in multipliers in the MCM module. Individual constant multiplication outputs are transferred by structural adders (SAs) and delay elements.

Fig 1: Finite Impulse Response filter having a phase which is linear and uniform arrangement :Direct method

Fig 2: Finite Impulse Response filter having a phase which is linear and uniform arrangement:Transposed Method Design of Finite Impulse Response filter has the adjustments in bit thickness of filter factors are critical,that includes serious influence in the space price of arithmetic units and registers. It is applicable to provide accurately rounding resulted in which the all faults generated by quantization and rounding has no upwards for 1 unit of final position that is the graded for LSB results. This paper offers small-range Finite Impulse Response filter designs found in direct construction as Figure.1 with accurately rounded shortened multiplier. In that Multiple Constant Multipliers Accumulators block was designed with gathering every PP in which unwanted Partial Products bits have been deleted excluding disturbing last result accuracy.

# 2. LITERATURE REVIEW

[1] C. Pan, Z. Wang, and C. Sechen, "High speed and power efficient compression of partial products and vectors,". A high speed and power efficient compression algorithm for an arbitrarily shaped array of partial products and vectors is presented. A minimum hard-ware usage algorithm for an arbitrarily shaped array of vectors was developed. Finally, a new delay-based addertype selection and CSA-tree wiring algorithm is proposed. This new compression network synthesis (CNS) algorithm was tested on several industrial DSP blocks for a variety of process technologies. [2] Mohanty, B. K., &Meher, P. K. (2013). A high-performance-energy-efficient architecture for FIR adaptive filter based on new distributed arithmetic formulation of block LMS algorithm. Itpresent an efficient distributed-arithmetic (DA) formulation for the implementation of block least mean square (BLMS) algorithm. The proposed DA-based design uses a novel look-up table (LUT)-sharing technique for the computation of filter outputs and weight-increment terms of BLMS algorithm. Besides, it offers significant saving of adders which constitute a major component of DA-based structures

# 3. PROPOSED WORK

This paper depicts the construction of digital FIR filters utilizes better version of truncated multiplier which needs lower number of multipliers and adders.

# **3.1 PROPOSED ARCHITECTURE:**

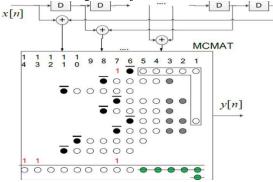

Fig 3 depicts the structure for Multiple Constant Multiplier/accumulators including the shortening which deletes the irrelevent partial product bits. Indelible PPBs are indicated in the L-shape block with white circles . Gray circles represents cancellation for Partial Product bits. The crossed circles indicates, the rounding of the resultant bits after PP compression. The offset, bias constants and sign bit adjustments all are indicated in the final row of the PPB matrix.

# Fig. 3Inclusive FIR filter stucture with MCMA using properly round off shortening

Low-price FIR filter solutions constructed with direct model are presented, having properly round off shortened multipliers. Multiple Constant Multiplier/accumulators block was created with aggregating every PP and deleting any extraneous partial product bits beyond disturbing output last accuracy. To lower hardware price while still meeting the frequency response criterion, bit thickness for every filter variables was decreased via shortened which is not uniform having different periods of word. Since space price for delay elements in flip flop was lower than transcribed version , the basic FIR structure with MCMA is used

#### 3.4 PERFORMANCE EVALUATION

Power and area performace evaluation has depicted in the following figures

| anon mas aspisioa m m            |          |      | -0  |         |         |      |          |       |

|----------------------------------|----------|------|-----|---------|---------|------|----------|-------|

| Total Number Slice Registers:    | 363      | out  | of  | 13,824  | 2*      |      |          |       |

| Number used as Flip Flops:       |          |      |     | 22      |         |      |          |       |

| Number used as Latches:          |          |      |     | 341     |         |      |          |       |

| Number of 4 input LUTs:          | 320      | out  | of  | 13,824  | 2%      |      |          |       |

| Logic Distribution:              |          |      |     |         |         |      |          |       |

| Number of occupied Slices:       |          |      |     |         | 207 ou  | t of | 6,912    | 2%    |

| Number of Slices containing      | only re. | late | d 1 | ogic:   | 207 ou  | t of | 207      | 100%  |

| Number of Slices containing      | unrelate | ed l | ogi | 3:      | 0 ou    | t of | 207      | 0%    |

| *See NOTES below for an          | explanat | tion | of  | the eff | ects of | unre | elated ( | .ogic |

| Total Number of 4 input LUTs:    | 320      | out  | of  | 13,824  | 2%      |      |          |       |

| Number of bonded IOBs:           | 16       | out  | of  | 325     | 4%      |      |          |       |

| IOB Flip Flops:                  |          |      |     | 8       |         |      |          |       |

| IOB Latches:                     |          |      |     | 8       |         |      |          |       |

| Number of GCLKs:                 | 1        | out  | of  | 4       | 25%     |      |          |       |

| Number of GCLKIOBs:              | 1        | out  | of  | 4       | 25%     |      |          |       |

|                                  |          |      |     |         |         |      |          |       |

| Total equivalent gate count for  | design:  | 3,5  | 905 |         |         |      |          |       |

| Additional JTAG gate count for 3 | 10Bs: 83 | 16   |     |         |         |      |          |       |

| Peak Memory Usage: 141 MB        |          |      |     |         |         |      |          |       |

Fig 4 Area of proposed work

| Power summary:                     | I(mA) | P(mW) |

|------------------------------------|-------|-------|

| Total estimated power consumption: |       | 54    |

| Vccint 1.80V:                      | 26    | 48    |

| Vcco33 3.30V:                      | 2     | 7     |

| Clocks:                            | 11    | 20    |

| Inputs:                            | 0     | 1     |

| Logic:                             | 0     | 0     |

| Outputs:                           |       |       |

| Vcco33                             | 0     | 0     |

| Signals:                           | 0     | 0     |

| Quiescent Vccint 1.80V:            | 15    | 27    |

| Quiescent Vcco33 3.30V:            | 2     | 7     |

#### Fig 5 Power of proposed work

### 4. **RESULTS**

As a result, a FIR filter is developed using a faithfully rounded truncated multiplier to save power and space in the multiplier and adder.

| PARAMETERS  | EXISTING<br>SYSTEM<br>(Constant<br>correction<br>truncation) | PROPOSED<br>SYSTEM<br>(Improved version<br>of truncation) |

|-------------|--------------------------------------------------------------|-----------------------------------------------------------|

| Gate counts | 4304                                                         | 3905                                                      |

| Area        | 328                                                          | 320                                                       |

| Power       | 59mw                                                         | 54mw                                                      |

#### Table.1. Performance Parameter Results

#### 5. CONCLUSION

The improvement in coefficient bit width in finite impulse response filter has been studied in this paper.Direct FIR architectures with accurately rounded MCMAT result in a smaller area and lower power consumption. The total number of similar gate counts and power in the present truncation system are 4304 and 59mW, respectively. In comparison to the existing method, the proposed truncation system produces better results.

#### 6. FUTURE SCOPE

In the future, the truncated multiplier will be utilised in conjunction with a 5:2 compressor to decrease the count of half adders to achieve an area reduction.

# 7. **REFERENCES**

[1] Z. Wu, Z. Huang and Z. Wang, "Research of Blind Equalization Technology of Coherent Optical Communication Based on Decidion Optimization," 2021 2nd Information Communication Technologies Conference (ICTC), 2021, pp. 139-144.

[2]K. A. Rao, A. Kumar and N. Purohit, "Efficient Implementation for 3-Parallel Linear-Phase FIR Digital Odd Length Filters," 2020 IEEE 4th Conference on Information & Communication Technology (CICT), 2020, pp. 1-6

[3] V. DeBrunner and L. S. DeBrunner, "How the Sampling Rate Impacts Wordlength Selection for FIR Filter Implementations," 2020 54th Asilomar Conference on Signals, Systems, and Computers, pp. 1291-1294, June 2020.

[4] R.P Meenaakshi Sundhari(2019) "An efficient implementation of low power approximate compressor-based multiplier for cognitive communication systems", International Journal of communication Systems, 2019, vol. 35

[5] B. S. M. Ali, Z. K. Farej and A. M. Ibrahim, "Implementing FIR Filters using Arduino Due Platform for Educational Purposes," 2019 2nd International Conference International Conference on Acoustics, Speech and Signal Processing (ICASSP), pp.1140-1144, Apr2018on Engineering Technology and its Applications (IICETA), 2019, pp. 49-54.

[6] K. J. Ahmed, B. Yuan and M. J. Lee, "High-Accuracy Stochastic Computing-Based FIR Filter Design," 2018 IEEE.

[7]Sharma P, Gupta M (2015) Area-efficient imlementation of heterogeneous adder and Its application in FIR filter. Int J Res Electron ComputEng 3:1–5

[8] Manoj Kumar K, Dr Meghana Kulkarni.(2015)" Implementation of high speed low power Vedic multiplier using reversible logic" International Journal of Advance Research In Science And Engineering http IJARSE, Vol. No.4, Issue 03,

[9] Yagain, D., & Krishna, A. V. (2014). Design of synthesizable, retimed digital filters using FPGA based path solvers with MCM approach: comparison and CAD tool. VLSI Design, 2014, 11.

[10] C. Pan, Z. Wang (2013) "High speed and power efficient compression of partial products and vectors," J. Algorithms Optim., Oct., vol. 1, no. 1, pp. 39–54.

[11] S.Kannadhasan, R.Nagarajan and R.Banupriya, Performance Improvement of an ultra wide band antenna using textile material with a PIN diode, Textile Research Journal, DOI: 10.1177/00405175221089690journals.sagepub.com/home/trj

[12] D. Shi and Y. J. Yu, "Design of linear phase FIR filters with high probability of achieving minimum number of adders," IEEE Trans. Circuits Syst.I, Reg. Papers, vol. 58, no. 1, pp. 126–136, Jan. 2011.

[13] Guo, R., &DeBrunner, L. S. (2011). Two high-performance adaptive filter implementation schemes using distributed arithmetic. IEEE Transactions on Circuits and Systems II: Express Briefs, 58(9), 600-604.

[14] V. G. Oklobdzija, D. Villeger (1996) "A method for speed optimized partial product reduction and generation of fast parallel multipliers using an algorithmic approach," IEEE Trans. Comput., vol. 45, no. 3, pp. 294–306.

[15] Zhongde Wang, G.A Jullien and W.C Miller (1995), "A New Design Technique for column compression multipliers," in IEEE Transaction on Computers, vol.44, no.8, pp.962-970.

# **Biographies**

**Dr.R.P. Meenaakshi Sundhari** is currently working as a Professor in the Department of Electronics and Communication Engineering in P. A. College of Engineering and Technology, Pollachi,Coimbatore - District. She has received her Ph.D degree in Information and Communication Engineering from Anna University. She is having more than 32 years of experience in Teaching. Her area of specialization includes VLSI Design, Machine Learning, Communication networks, Signal and Image Processing. She has published more than 50 papers in various International Journals which includes 10 Scopus indexed journals and has presented more than 30 papers in both International and National Conferences.

**A.Fathimasaffana**, **D.Dharanya**, **E**.**Bridget Maria Helen** are a students of U.G Degree Scholars in the field of Electronics and Communication Engineering in P.A college of Engineering and Technology